# Low Voltage Multi-Channel Motor Driver

# 1 Features

- Multi-channel Motor Driver

- Dual Stepper Motor

- Single Brushed DC Motor

- Full, Half, 32 Micro-Steps and 64 Micro-Steps

- Built-in DC Motor Driver

- ±0.5A Maximum Drive Current

- Instruction Cache Function

- Pre-stores next instruction

- Standard I2C Interface

- Work Status Indication

- FLAG Pin

- Small Package and Footprint

- 20 Pin QFN(With Thermal Pad)

- Protection Features

- Under-voltage Lockout(UVLO)

- Thermal Shutdown(TSD)

# 2 Applications

- Robot

- Precision Industrial Equipment

- Camcorder

- Security Camera

- Cradle Head

- Head-shaking Machine

# 3 Description

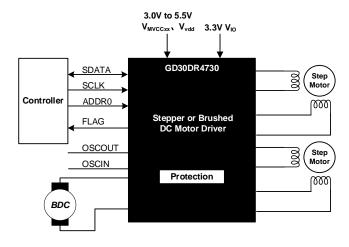

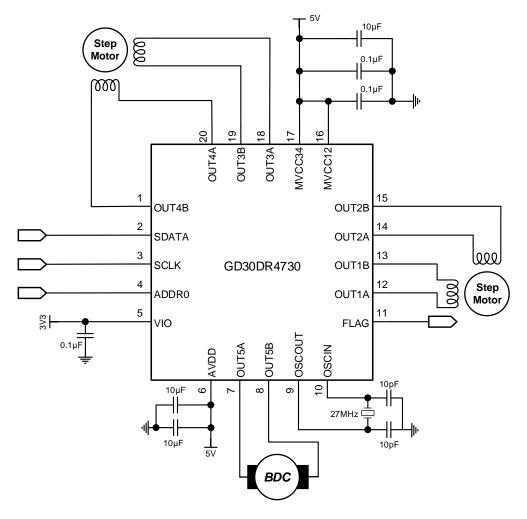

The GD30DR4730 is a multi-channel motor driver device that includes two stepper motor drives and one DC motor drive.

The maximum current of each channel is 0.5A. The device supporting two phase four wires, and four phase five wires stepper motors by I2C communication interface, which is compatible with 1.8V, 2.5V, 3.3V and 5.0V standard industrial interface. The operates on a motor power supply voltage from 3.0V to 5.5V.

Internal shutdown functions are provided for over temperature protection and under-voltage lockout protection.

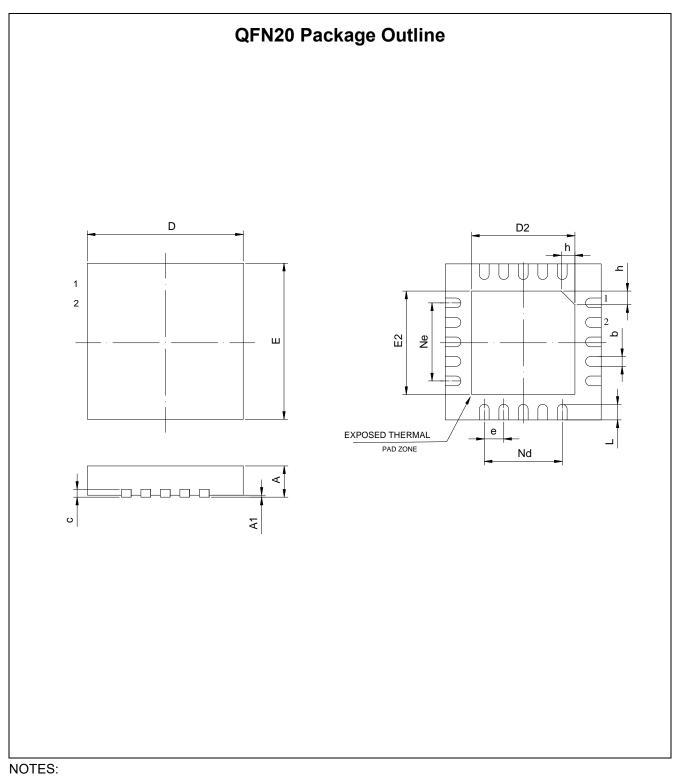

#### **Device Information<sup>1</sup>**

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| GD30DR4730  | QFN20   | 3.00 mm × 3.00 mm |

1. For packaging details, see Package Information section.

#### **Simplified Application Schematic**

# **Table of Contents**

| Features1 |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Appli     | cations                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Desci     | ription                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| le of C   | Contents                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Devic     | e Overview                                                                                                                                                                 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 4.1       | Pinout and Pin Assignment                                                                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 4.2       | Pin Description                                                                                                                                                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Paran     | neter Information                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 5.1       | Absolute Maximum Ratings                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 5.2       | Recommended Operation Conditions                                                                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 5.3       | Electrical Sensitivity                                                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 5.4       | Electrical Characteristics                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 5.5       | Timing Requirements                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Funct     | tional Description                                                                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 6.1       | Block Diagram                                                                                                                                                              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 6.2       | Operation                                                                                                                                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 6.3       | I2C Logic Description                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Appli     | cation Information                                                                                                                                                         | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 7.1       | Typical Application Circuit                                                                                                                                                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 7.2       | Design Example                                                                                                                                                             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 7.3       | Power Dissipation                                                                                                                                                          | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

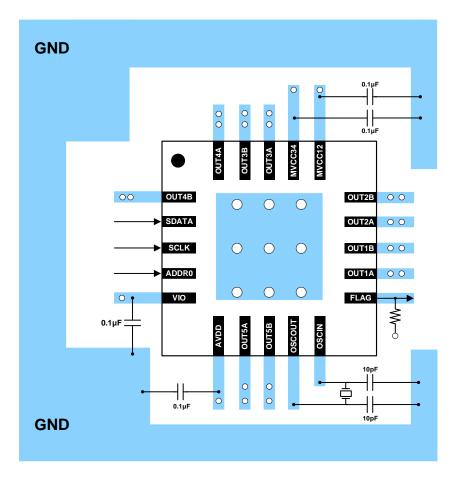

| Layou     | ut Guidelines and Example                                                                                                                                                  | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Packa     | age Information                                                                                                                                                            | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 9.1       | Outline Dimensions                                                                                                                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

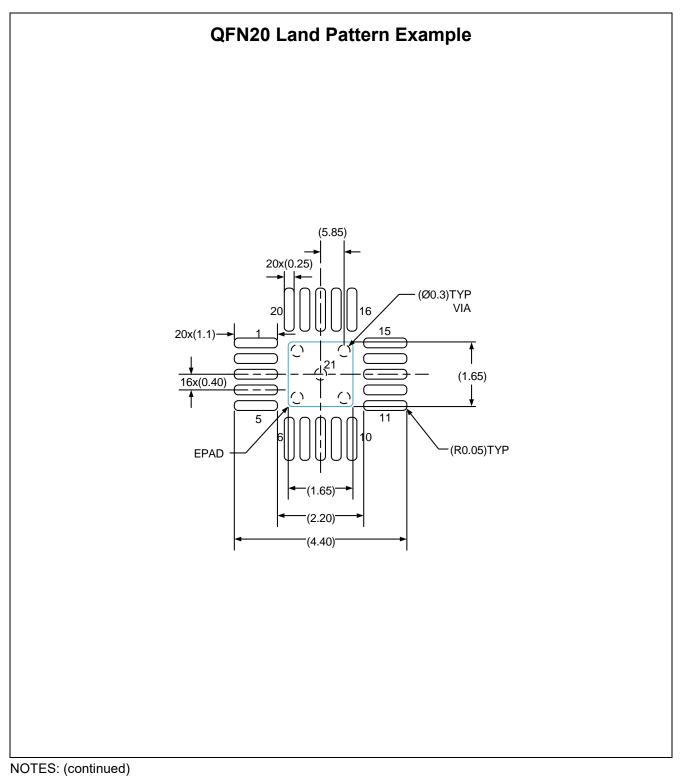

| 9.2       | Recommended Land Pattern                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Order     | ring Information                                                                                                                                                           | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|           | Revision History                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|           | Appli<br>Desc<br>4.1<br>4.2<br>Parar<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Func<br>6.1<br>6.2<br>6.3<br>Appli<br>7.1<br>7.2<br>7.3<br>Layou<br>Packa<br>9.1<br>9.2<br>Orde | Applications         Description         le of Contents         Device Overview         4.1         4.2         Pin Description         Parameter Information         5.1         Absolute Maximum Ratings         5.2         Recommended Operation Conditions         5.3       Electrical Sensitivity         5.4       Electrical Characteristics         5.5       Timing Requirements         Functional Description         6.1       Block Diagram         6.2       Operation         6.3       I2C Logic Description         7.1       Typical Application Circuit         7.2       Design Example         7.3       Power Dissipation         Layout Guidelines and Example         Package Information         9.1       Outline Dimensions         9.2       Recommended Land Pattern         Ordering Information |  |  |  |  |  |

# 4 Device Overview

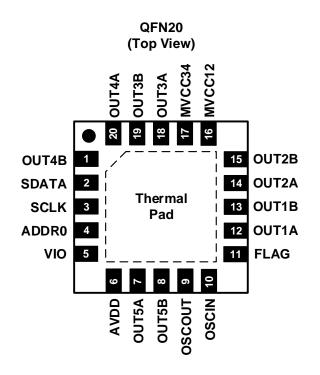

# 4.1 Pinout and Pin Assignment

# 4.2 Pin Description

| P      | IN  | PIN               | FUNCTION                         |  |  |

|--------|-----|-------------------|----------------------------------|--|--|

| NAME   | NUM | TYPE <sup>1</sup> | FUNCTION                         |  |  |

| OUT4B  | 1   | 0                 | Motor output 4B.                 |  |  |

| SDATA  | 2   | I/O               | I2C data line.                   |  |  |

| SCK    | 3   | I/O               | I2C clock line.                  |  |  |

| ADDR0  | 4   | I/O               | I2C address 0.                   |  |  |

| VIO    | 5   | Р                 | Interface power supply.          |  |  |

| AVDD   | 6   | Р                 | Logic power supply for DC motor. |  |  |

| OUT5A  | 7   | 0                 | Motor output 5A.                 |  |  |

| OUT5B  | 8   | 0                 | Motor output 5B.                 |  |  |

| OSCOUT | 9   | 0                 | Reference clock output.          |  |  |

| OSCIN  | 10  | I                 | Reference clock input.           |  |  |

| FLAG   | 11  | 0                 | Working Status Flag.             |  |  |

| OUT1A  | 12  | 0                 | Motor output 1A.                 |  |  |

| OUT1B  | 13  | 0                 | Motor output 1B.                 |  |  |

| OUT2A  | 14  | 0                 | Motor output 2A.                 |  |  |

| OUT2B  | 15  | 0                 | Motor output 2B.                 |  |  |

# Pin Description(continued)

| PI          | N       |                    | EUNCTION                   |

|-------------|---------|--------------------|----------------------------|

| NAME        | QFN20   | PINITPE            | FUNCTION                   |

| MVCC12      | 16      | Р                  | Power supply for motor 12. |

| MVCC34      | 17      | Р                  | Power supply for motor 34. |

| OUT3A       | 18      | O Motor output 3A. |                            |

| OUT3B       | 19      | 0                  | Motor output 3B.           |

| OUT4A       | 20      | 0                  | Motor output 4A.           |

| Thermal Pad | Thermal | G                  | GND for IC.                |

1. I = input, O = output, I/O = input/output, P = power, G = ground.

# 5 Parameter Information

# 5.1 Absolute Maximum Ratings

Exceeding the operating temperature range (unless otherwise noted)<sup>1</sup>

| SYMBOL           | PARAMETER                                           | MIN  | MAX     | UNIT |

|------------------|-----------------------------------------------------|------|---------|------|

| VIO              | Supply voltage of the interface                     | -0.3 | 5.5     | V    |

| VIN              | Digital input pin voltage <sup>4</sup>              | -0.3 | VIO+0.3 | V    |

| VFLAG            | Output Voltage Range                                | -0.3 | 6.0     | V    |

| MVCCxx           | Supply voltage for step motor                       | -0.3 | 5.5     | V    |

| AVDD             | Supply voltage for DC motor                         | -0.3 | 5.5     | V    |

| IMx(pulse)       | Instantaneous H bridge drive current for step motor | -0.6 | 0.6     | A/ch |

| OUTxA            | Motor Driver Output Current                         | -0.5 | 0.5     | A/ch |

| OUTxB            | Motor Driver Output Current                         | -0.5 | 0.5     | Aven |

| TA               | Operating ambient temperature <sup>3</sup>          | -40  | 85      | °C   |

| T <sub>stg</sub> | Storage temperature <sup>3</sup>                    | -55  | 125     | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. All voltage values are with respect to network ground terminal.

- 3. Except for the power disspation, operation ambient temperature, and storage temperature, all ratings are for T<sub>A</sub> = 25°C.

- 4. (VIO + 0.3)V must not be exceeded 5.5 V.

# 5.2 Recommended Operation Conditions

| SYMBOL <sup>1,2</sup> | PARAMETER                             | MIN  | TYP | MAX | UNIT |

|-----------------------|---------------------------------------|------|-----|-----|------|

| VIO                   | Supply voltage of the interface       | 1.8  |     | 5.5 | V    |

| AVDD                  | Supply voltage for DC motor           |      |     | 5.5 | V    |

| MVCCxx                | Supply voltage for step motor         |      |     | 5.5 | V    |

| I <sub>OUT</sub>      | Continuous motor drive output current | -0.5 |     | 0.5 | А    |

1. The device is not guaranteed to function outside of its operating conditions.

# 5.3 Electrical Sensitivity

| SYMBOL                | CONDITIONS                                                          | VALUE | UNIT |

|-----------------------|---------------------------------------------------------------------|-------|------|

| V <sub>ESD(HBM)</sub> | Human-body model (HBM), ANSI/ESDA/JEDEC JS-001-2017 <sup>1</sup>    | ±4000 | V    |

| V <sub>ESD(CDM)</sub> | Charge-device model (CDM), ANSI/ESDA/JEDEC JS-002-2022 <sup>2</sup> | ±2000 | V    |

1. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

2. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 5.4 Electrical Characteristics

MVCC12 = MVCC34 = AVDD = 5.0V, VIO = 3.3V,  $T_A = 25^{\circ}C \pm 2^{\circ}C$  (unless otherwise noted).

| SYMBOL                 | PARAMETER                                 | CONDITIONS                                    | MIN                  | TYP  | MAX                  | UNIT |

|------------------------|-------------------------------------------|-----------------------------------------------|----------------------|------|----------------------|------|

| POWER SI               | JPPLY                                     |                                               |                      |      |                      |      |

| V <sub>VDD</sub>       | AVDD and DC Motor supply voltage          |                                               | 3.0                  |      | 5.5                  | v    |

| VDD                    | range                                     |                                               | 5.0                  |      | 5.5                  | v    |

| Vvio                   | VIO supply voltage range                  |                                               | 1.8                  |      | 5.5                  | V    |

| VMVCCxx                | Step Motor supply voltage range           |                                               | 3.0                  |      | 5.5                  | V    |

| AVDDstandby            | AVDD supply current on standby            | No load                                       |                      | 1.2  |                      | mA   |

| DIGITAL-L              | EVEL INPUT & OUTPUT                       |                                               |                      |      |                      |      |

| VIL                    | Low-level input                           |                                               | -0.3                 |      | 0.31×V <sub>IO</sub> | V    |

| VIH                    | High-level input                          |                                               | 0.42×V <sub>IO</sub> |      | V <sub>IO</sub> +0.3 | V    |

| fclk                   | Input clock                               |                                               | 5                    | 27   | 30                   | MHz  |

| STEPPER                | MOTOR DRIVER                              | •                                             |                      |      |                      |      |

| R <sub>DS(ON)_ST</sub> | HS+LS FET on resistance                   | I <sub>O</sub> = 300mA, T <sub>J</sub> = 25°C |                      | 1.1  |                      | Ω    |

| ILEAK_ST               | H bridge leak current                     | V <sub>OUTx</sub> = 0V                        |                      |      | 0.8                  | μA   |

| DC MOTO                | R DRIVER                                  |                                               |                      |      |                      |      |

| Rds(on)_st             | HS+LS FET on resistance                   | Io = 200mA, TJ = 25°C                         |                      | 1.4  |                      | Ω    |

| I <sub>LGK_ST</sub>    | H bridge leakage current                  | V <sub>OUTx</sub> = 0V                        |                      |      | 0.7                  | μA   |

| PWM OUT                |                                           |                                               |                      |      |                      |      |

| VFLAG                  | Output saturation voltage                 | I = 5mA                                       |                      |      | 200                  | mv   |

| ILGK_FLAG              | Output leakage current                    |                                               |                      |      | 0.7                  | μA   |

| PROTECT                |                                           |                                               |                      |      |                      |      |

| TTSD                   | Thermal shutdown temperature <sup>1</sup> |                                               |                      | 155  |                      | °C   |

| T <sub>HYS</sub>       | Thermal shutdown hysteresis <sup>1</sup>  |                                               |                      | 25   |                      | °C   |

| SUPPLY V               | OLTAGE MONITOR CIRCUIT                    | 1                                             | I                    |      |                      |      |

| Vrst_on                | AVDD Reset operation                      |                                               |                      | 2.70 |                      | V    |

| V <sub>RST_HYS</sub>   | AVDD Reset hysteresis                     |                                               |                      | 0.20 |                      | V    |

| V <sub>ST_ON</sub>     | MVCCxx Reset operation                    |                                               |                      | 2.70 |                      | V    |

| Vst_hys                | MVCCxx Reset hysteresis                   |                                               |                      | 0.20 |                      | V    |

1. Not tested in production; based on design and characterization data.

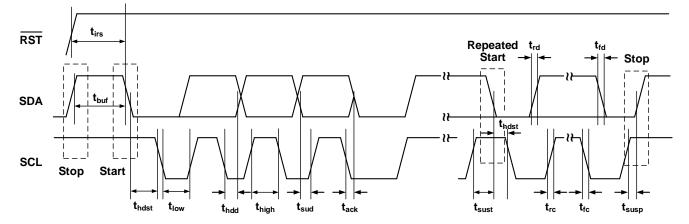

# 5.5 Timing Requirements

### 5.5.1 I2C Timing characteristics

| T <sub>4</sub> = 25℃ | VIO = 3.3V | AVDD = 5V                               | CI = 20  nF | Flunless | otherwise noted). |

|----------------------|------------|-----------------------------------------|-------------|----------|-------------------|

|                      |            | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | , OL 20 PI  |          |                   |

| SYMBOL                            | PARAMETER                                                                               | CONDITIONS | MIN | TYP | MAX  | UNIT |

|-----------------------------------|-----------------------------------------------------------------------------------------|------------|-----|-----|------|------|

| <b>f</b> scl                      | SCL input cycle                                                                         |            |     |     | 400  | kHz  |

| t <sub>irs</sub>                  | RST's rising edge to start                                                              |            | 500 |     |      | μs   |

| t <sub>buf</sub>                  | Bus idle time during conversion                                                         |            | 4.7 |     |      | μs   |

| t <sub>hdst</sub>                 | nitial conditional hold time before<br>he first clock pulse 4.0                         |            |     |     |      | μs   |

| t <sub>low</sub>                  | Clock low time                                                                          |            | 4.7 |     |      | μs   |

| thigh                             | Clock high time                                                                         |            | 4.0 |     |      | μs   |

| t <sub>sust</sub>                 | Establishment time of repeated start condition                                          |            | 4.7 |     |      | μs   |

| t <sub>hdd</sub>                  | Holding time from falling edge of SCL to SDA (note)                                     |            | 10  |     |      | ns   |

| t <sub>sud</sub>                  | Settling time from SDA to SCL rising edge                                               |            | 250 |     |      | ns   |

| t <sub>rc</sub> , t <sub>rd</sub> | Rising time of SCL and SDA                                                              |            |     |     | 1000 | ns   |

| t <sub>fc</sub> , t <sub>fd</sub> | Falling time of SCL and SDA                                                             |            |     |     | 300  | ns   |

| t <sub>susp</sub>                 | Establishment time of end condition                                                     |            | 4.7 |     |      | us   |

| t <sub>ack</sub>                  | Delay time from falling edge of SCL     300     1000       to response     300     1000 |            |     |     | 1000 | ns   |

1. The data must be kept for enough time to bridge the transition time  $t_{fc}$  on SCL.

Figure 1. I2C Bus Timing Diagram

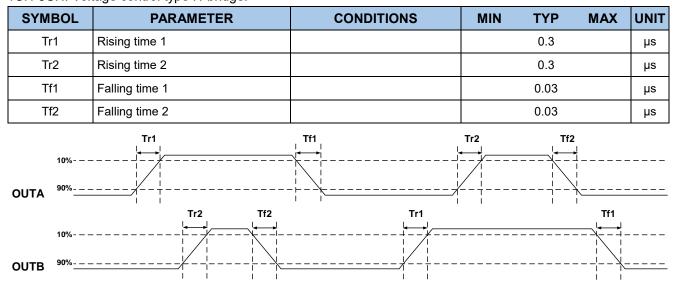

#### 5.5.2 Output Timing characteristics

$T_A = 25^{\circ}$ C, VIO = 3.3V, AVDD = MVCC = 5.0V, and insert 50 $\Omega$  between output pins(unless otherwise noted). 1CH-5CH: Voltage control type H-bridge.

Figure 2. Output Timing Diagram for GD30DR4730

# 6 Functional Description

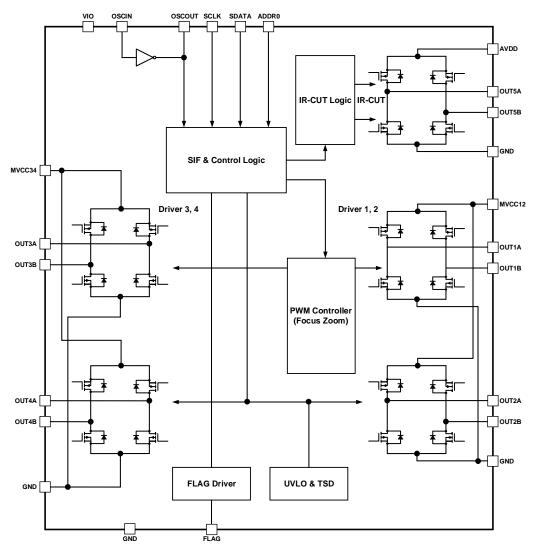

### 6.1 Block Diagram

Figure 3. GD30DR4730 Functional Block Diagram

### 6.2 Operation

The GD30DR4730 is a multi-channel motor driver integrated chip that works under low input voltage with a total of 5 groups of drive output channels. Four groups of motor drive outputs control the X axis and Y axis of the PZT motor with independent quadrature SPWM. Each group of output channels is composed of 4 MOSFETs, and the internal resistance is  $1.1\Omega$ . One set of motor drive output ports control IR cut, and conduct internal resistance  $1.4\Omega$ . Using I2C control, it is more convenient and accurate to control the motor speed and movement. A variety of protection functions can prevent the equipment against failure occurs.

### 6.2.1 PZT Control

The GD30DR4730 can control the X-axis and Y-axis of the PZT motor When working in the number of steps

controls the quadrature SPWM mode, also called manual control mode. It can work according to the set target number of turns and phase.

### 6.2.2 IR-Cut Control

The GD30DR4730 can control IR-Cut at the same time. It can support direction switching at any time. Three working states can be selected: Forward, Reverse and Brake.

### 6.2.3 VIO Under-voltage Lockout (UVLO)

If at any time the voltage on the VIO pin falls below the under-voltage-lockout threshold voltage, all FETs in the H-bridge will be disabled. Operation resumes when VIO rises above the UVLO threshold.

#### 6.2.4 Thermal Shutdown (TSD)

If the junction temperature exceeds safe limits, all FETs in the H-bridge are disabled. After the junction temperature has fallen to a safe level, operation automatically resume.

### 6.3 I2C Logic Description

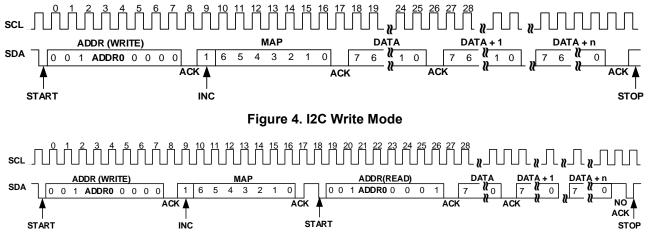

The GD30DR4730 is controlled by I2C communication. SDATA is bidirectional data line, and SCK is clock input. Figure 4 and show the signal timing of a write cycle and a read cycle, respectively. When the clock signal is high, SDATA has a falling edge as the starting condition; When the clock signal is high, the rising edge of SDATA is used as the end condition. All other changes in SDATA occur when the clock signal is low.

In the communication of GD30DR4730, after the initial condition, the first byte (ADDR) consisting of a 7-bit chip address and a 1-bit read/write bit (high for reading and low for writing) is sent to GD30DR4730. The first 3 bits of the 7-bit address are fixed 001, the last 3 bits are fixed 000, the 4th address is controlled by ADDR0 pin, and the 8th bit of the address is read/write. If it is a "write" operation, the next byte contains the register address pointer (MAP), which is used to select the register to be read or written. If it is a "read" operation, the contents of the register pointed by the MAP will be output. MAP is automatically incremented, and the data in the register will appear in turn. Each byte is separated by an acknowledge bit (ACK). GD30DR4730 outputs the reply bit after each input byte reading, and the microcontroller sends the reply bit to GD30DR4730 after each transmitted byte.

#### Figure 5. I2C Read Mode

Note that MAP bytes cannot be set during read operations, so a terminated write operation is required as a header

code. As shown in Figure 4, when a stop code is sent as a response to the MAP byte, the write operation is terminated.

| ADDRESS | D7              | D6              | D5                                 | D4         | D3            | D2       | D1       | D0       |

|---------|-----------------|-----------------|------------------------------------|------------|---------------|----------|----------|----------|

| 00H     | MOTORSEL        | MOTIONPLS       | CHIP ID A_F                        |            |               | A_PAUSE  | B_PAUSE  | CMD_RS   |

| 01H     |                 |                 |                                    | A_CYCLE[7: | 0]            |          |          |          |

| 02H     | A_MOI           | DE[1:0]         |                                    |            | A_CYCLE[      | 13:8]    |          |          |

| 03H     |                 | A_PULSE[7:      |                                    |            |               |          |          |          |

| 04H     | A_EN            | A_RT            | A_EXL                              |            |               | A_PULSE  | E[11:8]  |          |

| 05H     |                 | B_CYCLE[7:0]    |                                    |            |               |          |          |          |

| 06H     | B_MOI           | B_MODE[1:0]     |                                    |            | B_CYCLE[      | 13:8]    |          |          |

| 07H     |                 | B_PULSE[7:0]    |                                    |            |               |          |          |          |

| 08H     | B_EN            | B_RT            | B_EXL                              |            | B_PULSE[11:8] |          |          |          |

| 09H     | A_START         | B_START         | A_MS[0]                            | DC_SRC     | DC_C          | T[1:0]   | PWM_CH   | IOP[1:0] |

| C0AH    | CACHE_PWM       |                 |                                    | PWM        | _DUTY[6:0]    |          |          |          |

| 0BH     | A_MS[1]         | A_BUSY          | OTP_ERR                            | A_WORK     |               | A_STEPS_ | CU[11:8] |          |

| 0CH     |                 | A_STEPS_CU[7:0] |                                    |            |               |          |          |          |

| 0DH     | B_MS[1]         | B_BUSY          | SY B_MS[0] B_WORK B_STEPS_CU[11:8] |            |               |          |          |          |

| 0EH     | B_STEPS_CU[7:0] |                 |                                    |            |               |          |          |          |

| 0FH     |                 | A_PPW           | /[3:0]                             |            |               | B_PPW    | [3:0]    |          |

#### Table 1. Register Map

1. In the register table, prefixes A\_, B\_ and DC\_ correspond to A-channel, B-channel and DC motor channel registers respectively.

2. A channel is defined as the output driven by the combination of 1 channel and 2 channels, and B channel is defined as the output driven by the combination of 3 channels and 4 channels.

3. After RESET including power-on reset and reset through CMD\_RS register, all registers are set to the initial state, and the default value is 0.

4. For MODE, CYCLE, EN and RT registers, the written data will be valid before the PULSE register is enabled, and will be determined after the address where the PULSE register is located is written. MODE, CYCLE, EN, RT and PULSE registers have cache registers, but other register groups have no cache registers.

5. The data written into the registers of PAUSE, PWM\_CHOP, DC\_CT and PWM\_DUTY will take effect immediately after the data written into their addresses is completed.

#### Table 2. Register List

| ADDRESS          | REGISTER NAME/BIT WIDE | E FUNCTION                                                                    |  |  |  |

|------------------|------------------------|-------------------------------------------------------------------------------|--|--|--|

|                  | CMD_RS                 | Resetting registers                                                           |  |  |  |

|                  | B_PAUSE                | B-channel rotation pause                                                      |  |  |  |

| 0.011            | A_PAUSE                | A-channel rotation pause                                                      |  |  |  |

| 00H              | CHIP ID                | Chip identifier                                                               |  |  |  |

|                  | MOTIONPLS              | Select FLAG port output signal.                                               |  |  |  |

|                  | MOTORSEL               | Selection of driving mode of stepping motor                                   |  |  |  |

| 01H              | A_CYCLE[7:0]           |                                                                               |  |  |  |

| 0011             | A_CYCLE[13:8]          | A-channel motor operating frequency                                           |  |  |  |

| 02H              | A_MODE[1:0]            | A-channel stepping mode                                                       |  |  |  |

| 03H              | A_PULSE[7:0]           |                                                                               |  |  |  |

|                  | A_PULSE[11:8]          | A-channel stepping pulse number                                               |  |  |  |

| 0.411            | A_EXL                  | A Channel Pre/Post Excitation Time Length                                     |  |  |  |

| 04H              | A_RT                   | A-channel motor rotation direction                                            |  |  |  |

|                  | A_EN                   | A-channel drive enable                                                        |  |  |  |

| 05H              | B_CYCLE[7:0]           |                                                                               |  |  |  |

| 0011             | B_CYCLE[13:8]          | B-channel motor operating frequency                                           |  |  |  |

| 06H              | B_MODE[1:0]            | B-channel stepping mode                                                       |  |  |  |

| 07H              | B_PULSE[7:0]           |                                                                               |  |  |  |

|                  | B_PULSE[11:8]          | B-channel stepping pulse number                                               |  |  |  |

| 0011             | B_EXL                  | B Channel Pre/Post Excitation Time Length                                     |  |  |  |

| 08H              | B_RT                   | B-channel motor rotation direction                                            |  |  |  |

|                  | B_EN                   | B-channel drive enable                                                        |  |  |  |

|                  | PWM_CHOP[1:0]          | 5-channel PWM frequency                                                       |  |  |  |

|                  | DC_CT[1:0]             | 5-channel DC motor drive signal                                               |  |  |  |

| 0011             | DC_SRC                 | 5-channel input signal source                                                 |  |  |  |

| 09H              | A_MS[0]                | A-channel drive mode indication (read-only)                                   |  |  |  |

|                  | B_START                | B-channel drive start                                                         |  |  |  |

| A_START          |                        | A-channel drive start                                                         |  |  |  |

|                  | PWM_DUTY[6:0]          | 5-channel PWM duty cycle setting                                              |  |  |  |

| 0AH<br>CACHE_PWM |                        | CACHE status indication /PWM signal is output and selected through FLAG port. |  |  |  |

| 0BH              | A_WORK                 | A channel drive status indication (read-only)                                 |  |  |  |

Copyright © 2023, GigaDevice Semiconductor Inc. All Rights Reserved.

www.gigadevice.com

| ADDRESS | REGISTER NAME/BIT WIDE | FUNCTION                                                       |  |  |  |  |  |

|---------|------------------------|----------------------------------------------------------------|--|--|--|--|--|

|         | OTP_ERR                | Indication of over-temperature protection function (read-only) |  |  |  |  |  |

|         | A_BUSY                 | A-channel instruction buffer status (read only)                |  |  |  |  |  |

|         | A_MS[1]                | A-channel drive mode indication (read-only)                    |  |  |  |  |  |

|         | A_STEPS_CU[11:8]       | Current instruction running stone of shonnel A (read only)     |  |  |  |  |  |

| 0CH     | A_STEPS_CU[7:0]        | Current instruction running steps of channel A (read-only)     |  |  |  |  |  |

|         | B_WORK                 | B channel drive status indication (read-only)                  |  |  |  |  |  |

|         | B_MS[1:0]              | B-channel drive mode indication (read-only)                    |  |  |  |  |  |

| 0DH     | B_BUSY                 | B-channel instruction buffer status (read only)                |  |  |  |  |  |

|         | B_STEPS_CU[11:8]       | Current instruction running stone of shonnel A (read only)     |  |  |  |  |  |

| 0EH     | B_STEPS_CU[7:0]        | Current instruction running steps of channel A (read-only)     |  |  |  |  |  |

| 0FH     | B_PPW[3:0]             | B-channel PWM maximum duty cycle setting                       |  |  |  |  |  |

| UFF     | A_PPW[3:0]             | A-channel PWM maximum duty cycle setting                       |  |  |  |  |  |

### 6.3.1 Configuration register

#### 6.3.1.1 CMD\_RS: Resetting register

| D0 | CONDITION                 |

|----|---------------------------|

| 0  | reset (initial condition) |

| 1  | releasing reset           |

1. Resisters are reset to initial condition. You need to set this bit to 1 before you start configuring the other registers.

2. In the initial condition, outputs of constant voltage Driver 1  $\sim$  5ch are Hi-Z.

#### 6.3.1.2 PAUSE: Force a pause

| D2/D1 | MOTOR STATE                              |

|-------|------------------------------------------|

| 0     | Normal operation (initial state)         |

| 1     | Stop at the current position immediately |

1. After the PAUSE is set to "1" (stop), MODE, CYCLE, RT and EN are kept. After reset to 0, the motor can continue to run according to the original settings. The PULSE register will be cleared, you need to reset the PULSE register.

After the PAUSE is set to "1" (stop), you can set EN=0 to clear the number of unfinished steps, and PAUSE=0 to terminate the pause. Reset EN=1, PULSE, CYCLE, and RT parameters, set the corresponding start bit, and the motor will run according to the new parameters.

#### 6.3.1.3 MOTIONPLS: Select the type of FLAG signal

| D6 | DRIVE TYPE                         |

|----|------------------------------------|

| 0  | Running status indication          |

| 1  | Cache register status / PWM output |

Operation status indication: When a group of instructions of A/B channel run to an end (motor stops), the FLAG pin will output a square wave signal with a pulse width of 128\*f<sub>CLK</sub>, which can be used to inform the main controller that the current motor is in a stopped state.

2. Cache register status PWM output: If CACHE\_PWM is set to 1, and A\_EN or B\_EN is set to 1, the FLAG pin outputs PWM

signals defined by PWM CHOP and PWM DUTY; if set to 0, the FLAG pin outputs a PULSE with a width of 128 times the clock width when the values of the pulse and EN cache registers of any channel change from non-zero to zero. If both channels have this change from non-zero value to zero value (at different times), two pulses will be output at corresponding times through the FLAG pin.

3. "f<sub>CLK</sub>" is the clock frequency of the chip.

#### 6.3.1.4 MOTORSE: Select the motor drive type

| D7 | DRIVE TYPE                                  |

|----|---------------------------------------------|

| 0  | 2-phase 4-wire motor driver (initial state) |

| 1  | 4-phase 5-wire motor driver                 |

#### 6.3.1.5 CYCLE: Set the frequency of motor operation

| D13 | D12                              | D11 | D10 | D9     | D8      | D7      | D6      | D5    | D4     | D3 | D2 | D1       | D0 | IMPULSE<br>FREQUENCY               |

|-----|----------------------------------|-----|-----|--------|---------|---------|---------|-------|--------|----|----|----------|----|------------------------------------|

|     | 00_0000_0000_0000 ~ 00_0000_0111 |     |     |        |         |         |         |       |        |    |    | Disabled |    |                                    |

|     |                                  |     | 0   | 0_0000 | <u></u> | _0000 ^ | ~ 00_00 | 00_00 | 00_011 | 1  |    |          |    | (initial state is 0)               |

| 0   | 0                                | 0   | 0   | 0      | 0       | 0       | 0       | 1     | 0      | 0  | 0  | 0        | 0  | f <sub>CLK</sub> / (8×4×32)pps     |

| 0   | 0                                | 0   | 0   | 0      | 0       | 0       | 0       | 1     | 0      | 0  | 0  | 0        | 1  | f <sub>CLK</sub> / (9×4×32)pps     |

| 0   | 0                                | 0   | 0   | 0      | 0       | 0       | 0       | 1     | 0      | 0  | 0  | 1        | 0  | f <sub>CLK</sub> / (10×4×32)pps    |

|     | ~                                |     |     |        |         |         |         |       |        |    | ~  |          |    |                                    |

| 1   | 1                                | 1   | 1   | 1      | 1       | 1       | 1       | 1     | 1      | 1  | 1  | 1        | 0  | f <sub>CLK</sub> / (16382×4×32)pps |

| 1   | 1                                | 1   | 1   | 1      | 1       | 1       | 1       | 1     | 1      | 1  | 1  | 1        | 1  | f <sub>CLK</sub> / (16383×4×32)pps |

1. The specified CYCLE is valid for 1-2 phase and 2- phase excitation and micro-step subdivision modes.

2. The initial state only exists after the reset signal is released. If CYCLE is set to a value within the forbidden range (16'b 0000\_0000\_0000 ~ 16'b 0000\_0000\_0000\_0111), the motor will not operate and you need to make sure the cycle is set in the correct range.

3. fclk is the clock frequency provided to the main logic.

#### For example:

### input data = 16'b0000 0010 1110 1110, fcLK = 24[MHz] impulse frequency = 24[MHz]/(750×4×32) =250[pps] =31.25[Hz]

#### 6.3.1.6 MODE[1:0]: Setting of the operation mode

| D7 | D6 | OPERATION MODE                                   |

|----|----|--------------------------------------------------|

| 0  | 0  | 2-phase excitation full step (initial condition) |

| 0  | 1  | 32 Micro-step                                    |

| 1  | 0  | 1-2phase excitation  half step                   |

| 1  | 1  | 64 Micro-step                                    |

1. When changing the operation mode, do not set pulse number "0".

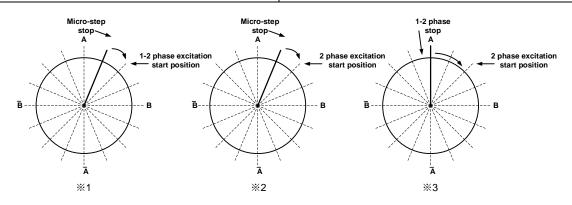

2. At the selection of Micro-step operation, 1-2 phase excitation, 2-phase excitation, the start position varies as shown below:

#### Table 3. The Selection of Micro-step Operation

| $BEFORE\;MODE\;\;\to\;\;AFORE\;MODE$    | OPERATION AT THE SELECTION OF MODE                                    |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------|--|--|--|

| $\mu$ step $\rightarrow$ 1-2 phase      | start from the next 1-2phase excitation position to stop position(%1) |  |  |  |

| GD30DR4730 Rev1.1 Copyright © 2023, Gig | aDevice Semiconductor Inc. 14                                         |  |  |  |

| $BEFORE\;MODE\;\to\;AFORE\;MODE$          | OPERATION AT THE SELECTION OF MODE                          |

|-------------------------------------------|-------------------------------------------------------------|

| u atan ang 2 nhasa                        | start from the next 2-phase excitation position to stop     |

| $\mu$ step $\rightarrow$ 2-phase          | position(%2)                                                |

| 32 micro-step $\rightarrow$ 64 micro-step | start from the stop position                                |

| 64 micro-step $\rightarrow$ 32 micro-step | start from the next 32 micro-step position to stop position |

| 1.2 mbass                                 | start from the next 2-phase excitation position to stop     |

| 1-2 phase $\rightarrow$ 2-phase           | position(%3)                                                |

| 1-2 phase $\rightarrow$ µ step            | start from the stop position                                |

| 2-phase $\rightarrow$ 1-2 phase           | start from the stop position                                |

| 2-phase $\rightarrow \mu$ step            | start from the stop position                                |

Figure 6. The Selection of Micro-step Operation

When the motor is set to backward rotation direction, it moves to the backward rotation direction.

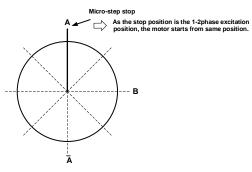

For  $\times 1$ ,  $\times 2$ ,  $\times 3$ , the motor moves from the stop position when the stop position is same as the position after the selection of mode.

Figure 7. %1 Example

| D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2  | D1 | D0 | PULSE NUMBER                 |   |   |  |   |                    |

|-----|-----|----|----|----|----|----|----|----|-----|----|----|------------------------------|---|---|--|---|--------------------|

| 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0(initial setting)           |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 1 (full step)                |   |   |  |   |                    |

| 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 0 | 0  | 1  | 1/2 (half step)              |   |   |  |   |                    |

| 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | I  | 1/8 (32 micro-step)          |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 1/16 (64 micro-step)         |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 2 (full step)                |   |   |  |   |                    |

| 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1  | 0  | 1 (half step)                |   |   |  |   |                    |

| 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | I  | 0  | 1/4 (32 micro-step)          |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 1/8 (64 micro-step)          |   |   |  |   |                    |

|     |     |    |    |    |    |    | ~  |    |     |    |    |                              |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 2047 (full step)             |   |   |  |   |                    |

| 0   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 1                            | 1 | 1 |  | 1 | 2047/2 (half step) |

| 0   |     | I  | 1  | I  |    | 1  | 1  | 1  | I   | 1  | I  | 2047/8 (32 micro-step)       |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 2047/16 (64 micro-step)      |   |   |  |   |                    |

|     |     |    |    |    |    |    | ~  |    |     |    |    |                              |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 4095 (full step)             |   |   |  |   |                    |

| 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 4095 (half step upper limit) |   |   |  |   |                    |

|     |     | 1  | 1  | I  | 1  | 1  | 1  | 1  |     | 1  |    | 4095/8 (32 micro-step)       |   |   |  |   |                    |

|     |     |    |    |    |    |    |    |    |     |    |    | 4095/16 (64 micro-step)      |   |   |  |   |                    |

#### 6.3.1.7 PULSE: Used to make setting of pulse number

1. step number = Pulse number × Number of driving mode steps.

#### For example:

A\_MODE ="10"(1-2 phase, half step), PULSE = 12'b0011\_1110\_1000, step number = 1000 × 1/2 = 500 A\_MODE ="11"(64 micro-step), PULSE = 12'b0011\_1110\_1000, step number = 1000 × 1/16 = 62.5

#### 6.3.1.8 EXL: Set the excitation time of the motor.

| D5 | EXCITATION TIME |

|----|-----------------|

| 0  | 0               |

| 1  | 1/2 x Pulse     |

1. When the excitation time is set to 0, there is no pre-excitation and post-excitation in the stepping channel.

2. When the excitation time is set to 1, the excitation time is 1/2 full step.

3. When EXL is set to 1: When EN changes from 0 to 1, pre-excitation takes effect; When EN changes from 1 to 0, the post excitation takes effect.

#### 6.3.1.9 RT: Setting of the pulse rotating direction

| D6 | DIRECTION                              |

|----|----------------------------------------|

| 0  | CW (forward rotation, initial setting) |

| 1  | CCW (backward rotation)                |

#### 6.3.1.10 EN: Setting of driver enable control

| D7 | STATION      |

|----|--------------|

| 0  | Hi-Z         |

| 1  | Normal drive |

1. When EN is set to 0, any data written to the PULSE register will be treated as "0".

#### 6.3.1.11 PWM\_CHOP: Setting of PWM chopping frequency

| D1 | D0 | CHOPPING FREQUENCY                               |

|----|----|--------------------------------------------------|

| 0  | 0  | FCHOP = f <sub>CLK</sub> / 128 (initial setting) |

| 0  | 1  | FCHOP = f <sub>CLK</sub> / 256                   |

| 1  | 0  | FCHOP = f <sub>CLK</sub> / 512                   |

| 1  | 1  | FCHOP = f <sub>CLK</sub> / 1024                  |

1. " $f_{CLK}$ " is the clock frequency of the chip.

#### 6.3.1.12 DC\_CT: Used to make setting of the statue of the driver

| D3 | D2 | STATUS OF THE DRIVER   |

|----|----|------------------------|

| 0  | 0  | Hi-Z (initial setting) |

| 0  | 1  | Forward rotation       |

| 1  | 0  | Backward rotation      |

| 1  | 1  | brake                  |

#### 6.3.1.13 DC\_SRC: Select the external or internal control

| D4 | STATE OF THE CONTROL                     |  |  |  |

|----|------------------------------------------|--|--|--|

| 0  | internal control (DC_CT、initial setting) |  |  |  |

| 1  | external control                         |  |  |  |

#### 6.3.1.14 START: Enable the A/B channel to start running.

| D7/D6 | ENABLED STATE                         |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|

| 0     | None (initial state)                  |  |  |  |  |

| 1     | A/B channel operation (self-clearing) |  |  |  |  |

1. This register bit is the start pulse of the A/B channel's running instruction. When it is set to 1, it will be reset to 0 after an SCLK. If the stepping motor is currently running, the instruction loads the settings (PULSE, CYCLE, etc.) into the cache.

#### 6.3.1.15 CACHE\_PWM: Setting the FLAG pin output signal mode.

| D7 | FLAG STATE(MOTIONPLS = 1)                                                                               |  |  |  |  |  |  |  |

|----|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0  | The pin directly outputs the state of the buffer register (PULSE, EN), and outputs a pulse with a clock |  |  |  |  |  |  |  |

| 0  | frequency of 128 times when there is a change from a non-zero value to a zero value.                    |  |  |  |  |  |  |  |

| 1  | When A_EN=1 or B_EN=1, the pin outputs PWM signals defined by PWM_CHOP and PWM_DUTY.                    |  |  |  |  |  |  |  |

#### 6.3.1.16 PWM\_DUTY: Setting PWM duty cycle of DC motor channel

| D6 | D5 | D4 | D3 | D2 | D1 | D0 | PWM DUTY CYCLE                  |

|----|----|----|----|----|----|----|---------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 128/128 ×100% (initial setting) |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1/128 ×100%                     |

|    |    |    | ~  |    |    |    | ~                               |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 127/128 ×100%                   |

1. The duty values are significantly influenced by turn ON or turn OFF time of the output driver, compared to the digital processing accuracy.

2. To avoid that, pay utmost attention to the design of duty values.

#### 6.3.1.17 PPW[3:0]: Set the peak pulse width of stepping driver.

| D7/D3 | D6/D2 | D5/D1 | D4/D0 | PWM DUTY CYCLE                  |

|-------|-------|-------|-------|---------------------------------|

| 0     | 0     | 0     | 0     | 128/128 ×100% (initial setting) |

| 0     | 0     | 0     | 1     | 1/16 ×100%                      |

|       | ~     | ~     |       | ~                               |

| 1     | 1     | 1     | 1     | 15/16 ×100%                     |

#### 6.3.1.18 Cache register

The chip has a built-in cache register that can temporarily register input instructions while the motor is running. After the motor completes the current task, it will continue to run the registered instructions.

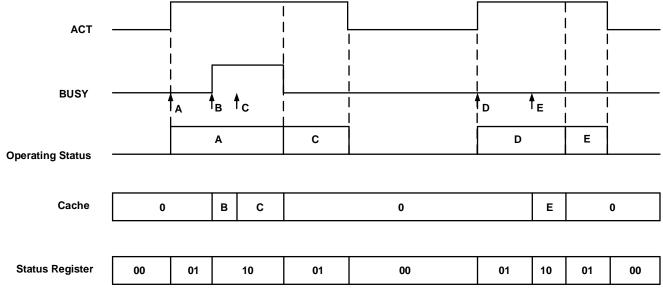

#### Figure 8. Cache Register

The operation instructions (MODE, CYCLE, RT, PULSE) of the stepping motor are determined after the writing of the address of the PULSE register is completed. When the current instruction runs, the re-entered data will be temporarily stored in the cache register and will be continued after the current instruction is completed. When the data has been registered in the cache, the newly input data can still be received, and the newly input data will overwrite the original data.

The status of the current cache register can be read by both setting MOTIONPLS to 1 and CACHE\_PWM to 0.

when the values of PULSE and EN cache registers of any channel change from non-zero values to zero values, the FLAG pin will output a pulse with a width of 128 times the clock width.

If both channels have this change from non-zero value to zero value (at different times), two pulses will be output through the FLAG pin.

### 6.3.2 Read-only Registers

#### 6.3.2.1 MS: Indicating the current motor drive mode

| D7 | D5 | INDICAING DRIVE MODE                 |

|----|----|--------------------------------------|

| 0  | 0  | 2 phase   full step(initial setting) |

| 0  | 1  | 32 micro-step                        |

| 1  | 0  | 1-2 phase   half step                |

| 1  | 1  | 64 micro-step                        |

#### 6.3.2.2 BUSY: Indicating the cache register status of the channel.

| D5 | INDICATING STATUS |  |  |  |

|----|-------------------|--|--|--|

| 0  | NO                |  |  |  |

| 1  | YES               |  |  |  |

#### 6.3.2.3 OTP\_ERR: Indicating the OTP status.

| D5 | INDICATING STATUS |  |  |  |

|----|-------------------|--|--|--|

| 0  | On work           |  |  |  |

| 1  | In OTP            |  |  |  |

# 6.3.2.4 STEP\_CU: Indicating the number of integer steps that the current instruction channel has completed.

| D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | STEP NUMBER            |                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                    |

|-----|-----|----|----|----|----|----|----|----|----|----|----|------------------------|------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--------------------|

|     |     |    |    |    |    |    |    |    |    |    |    | 1 (full step)          |                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                    |

| 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1                      | 1/2 (half step)  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                    |

| 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | I  | 1/8 (32micro-step)     |                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                    |

|     |     |    |    |    |    |    |    |    |    |    |    | 1/16 (64micro-step)    |                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                    |

|     | ~   |    |    |    |    |    |    |    |    |    |    |                        |                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                    |

|     |     |    |    |    |    |    |    |    |    |    |    | 2047 (full step)       |                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                    |

| 0   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1                      | 1                | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 4 | 1 | 1 | 4 |   | 1 | 1 | 2047/2 (half step) |