# 8-Channel DAS with 16-Bit、1 MSPS、Bipolar Input、

# **Simultaneous Sampling ADC**

# 1 Features

- GD30AD3380-I10: 16-bit, 1 MSPS ADC

- GD30AD3380-I05: 16-bit, 500 KSPS ADC

- 5 V single analog supply

- VDRIVE supply voltage:

- GD30AD3380-I10: 1.71 V to 3.6 V

- GD30AD3380-I05: 1.71 V to 5 V

- Selectable analog input range per channel

- GD30AD3380-I10 true bipolar hardware Mode: ±10 V, ±5 V

- GD30AD3380-I05 true bipolar hardware Mode: ±10 V , ±5 V

- GD30AD3380-I10 true bipolar software

Mode: ±12.5 V, ±10 V, ±5 V and ±2.5 V

- with 1 MΩ analog input impedance

- Flexible digital filter for oversampling application

- Flexible paraller/serial communication

interface

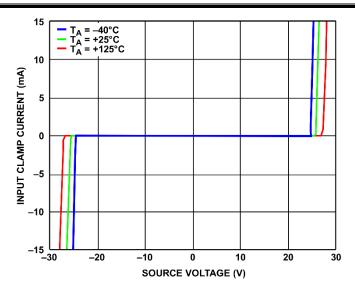

- ±25 V input clamp protection, 8 kV ESD

- Operating temperature range: -40 °C to +125 °C

# 2 Application

- Power line monitoring

- Protection relay

- Multiphase Motor Control

- Instrumentation and control systems

- Data Acquisition System

# 3 Description

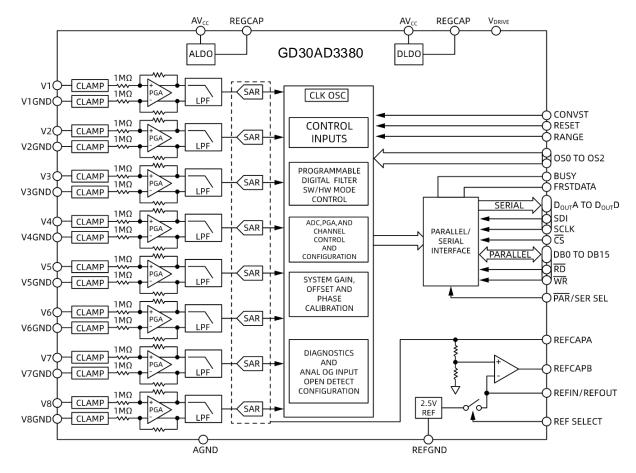

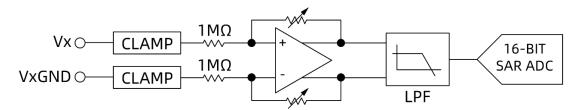

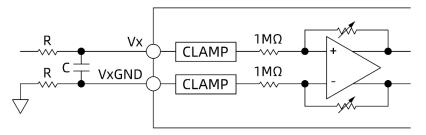

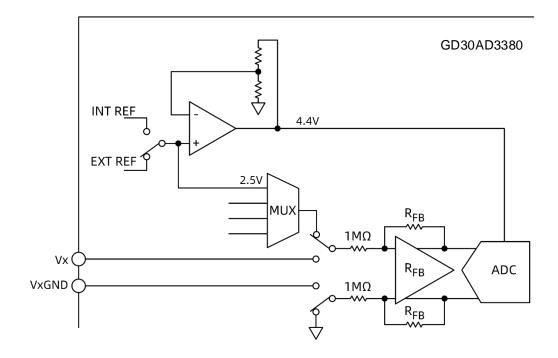

The GD30AD3380 is a 16-bit, synchronous sampling, analog-to-digital conversion data acquisition system (DAS) with 8 channels, each with built-in analog input clamp protection, programmable gain amplifier (PGA), low-pass filter and 16-bit successive approximation register (SAR) analog-to-digital converter (ADC). The GD30AD3380 also has built-in flexible digital filters, lowdrift 2.5V precision reference voltage source and reference voltage buffer (for driving ADC) and flexible parallel and serial interfaces.

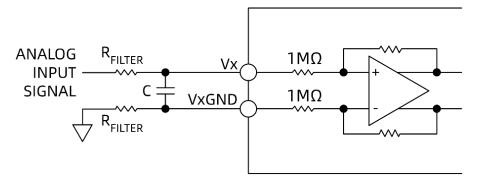

The GD30AD3380 operates from a single 5 V supply and supports  $\pm 12.5$  V ,  $\pm 10$  V ,  $\pm 5$  V , and  $\pm 2.5$  V true bipolar input ranges when all channels are sampled at a throughput rate of 1 MSPS (GD30AD3380-I10). Input clamp protection withstands voltages up to  $\pm 25$  V. The GD30AD3380 has a 1 M $\Omega$  analog input impedance, and the bipolar zero code is less than 100 LSB when the input signal is disconnected and pulled to ground through a 10 k $\Omega$  external resistor . Single-supply operation, on-chip filtering, and high input impedance eliminate the need for an external driver op amp (requires a bipolar supply). For applications with lower throughput rates, the GD30AD3380's flexible digital filter can be used to improve noise performance.

In hardware mode, GD30AD3380 is fully compatible with a mainstream model. GD30AD3380-I10 in software mode, the following advanced features can be used:

- Added ±12.5 V , ±2.5 V analog input range, selectable for each channel

- High bandwidth mode (200 kHz) , selectable per channel

- Additional oversampling (OS) options, up to OS×256

- System gain, system offset, and system phase calibration for each channel

# GD30AD3380

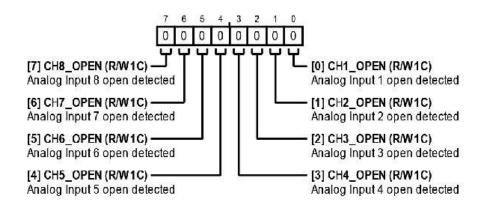

- Analog Input Open Detector

- Diagnostic Multiplexer

- Monitoring functions (Serial Peripheral Interface (SPI) invalid read / write, cyclic redundancy check (CRC), overvoltage and undervoltage events, busy blocking monitoring, and reset detection)

Note that throughout this data sheet, multifunction pins, such as the RD/SCLK pin, are referenced either by the full pin name or by a single function of the pin; for example, the SCLK pin means only that function is relevant. Additionally, the GD30AD3380-I05 only supports hardware mode, and all software mode-related features and functions that require configuration of registers are not supported.

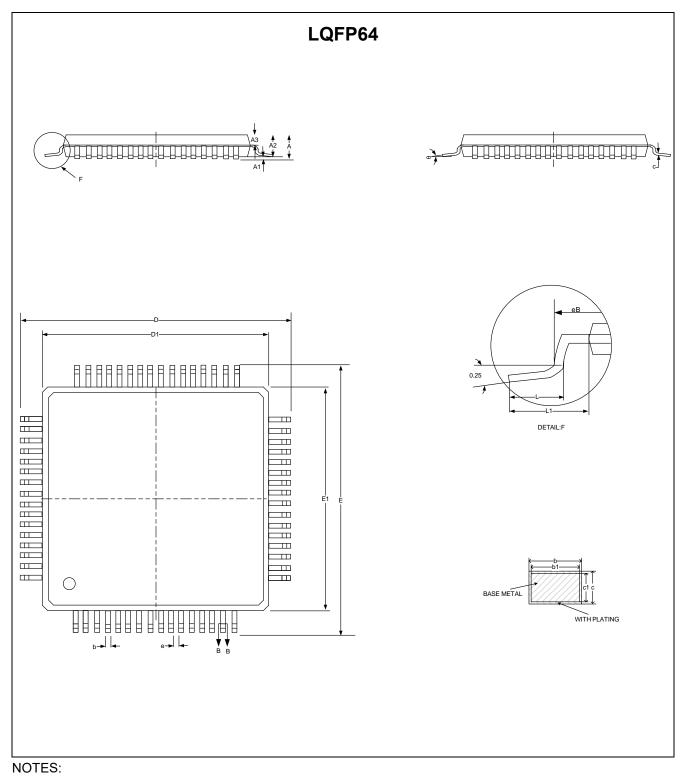

#### Device Information <sup>1</sup>

|    | PAR |           | ł  | PAC     | <b>KAGE</b> | BODY SIZE (NOM     |       |    |           |

|----|-----|-----------|----|---------|-------------|--------------------|-------|----|-----------|

|    | GE  | 030AD3380 |    | LQF     | P 64        | 10.00 mm × 10.00 m |       |    | 10.00 mm  |

| 1. | For | packaging | de | etails, | please      | е                  | refer | to | Packaging |

information section .

# Table of contents

| 1  |              | ires                                     |    |

|----|--------------|------------------------------------------|----|

| 2  |              | cation                                   |    |

| 3  |              | ription                                  |    |

|    |              | ontents                                  |    |

| 4  |              | ce Overview                              |    |

|    | 4.1          | Pinout and Pin Assignment                |    |

| 5  | 4.2          | Pin Description                          |    |

| 5  |              | neter information                        | -  |

|    | 5.1          | Absolute Maximum Ratings                 |    |

|    | 5.2          |                                          |    |

|    | 5.3          | GD30AD3380-I10 Electrical Characteristic |    |

|    | 5.4          | GD30AD3380-105 Electrical Characteristic |    |

|    | 5.5          | Timing Specifications                    |    |

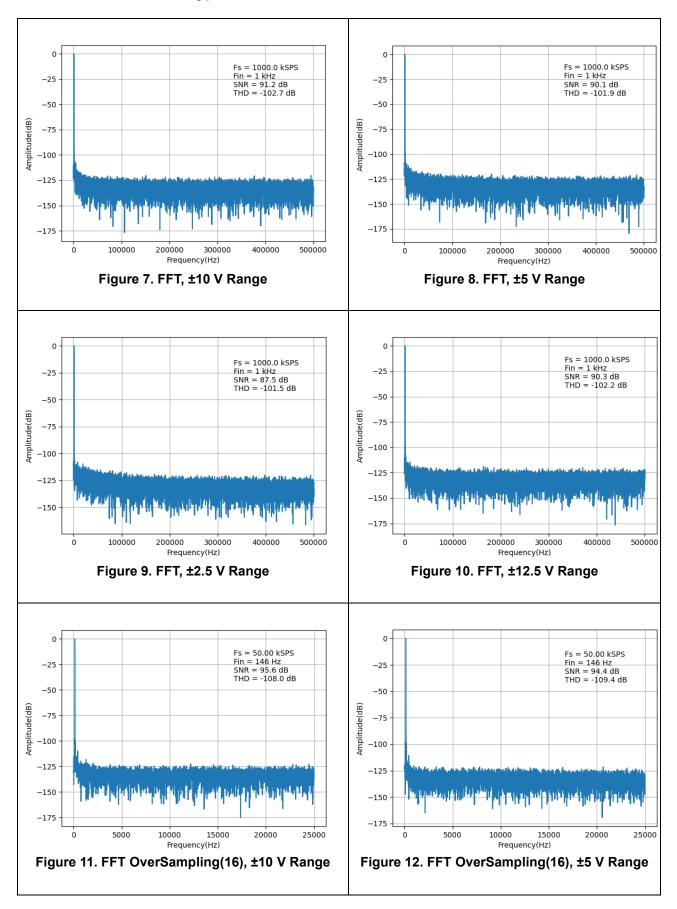

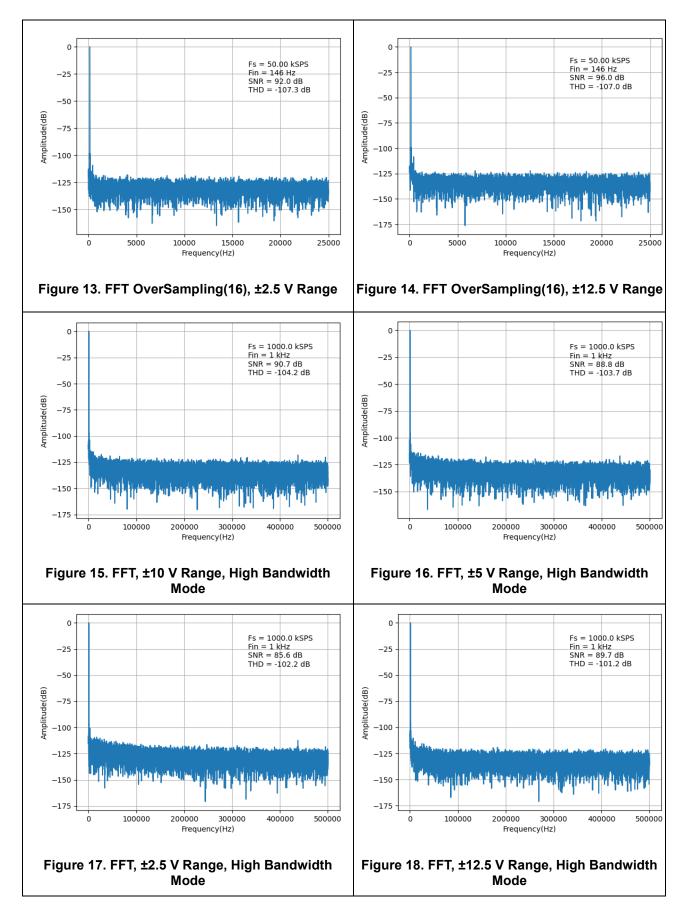

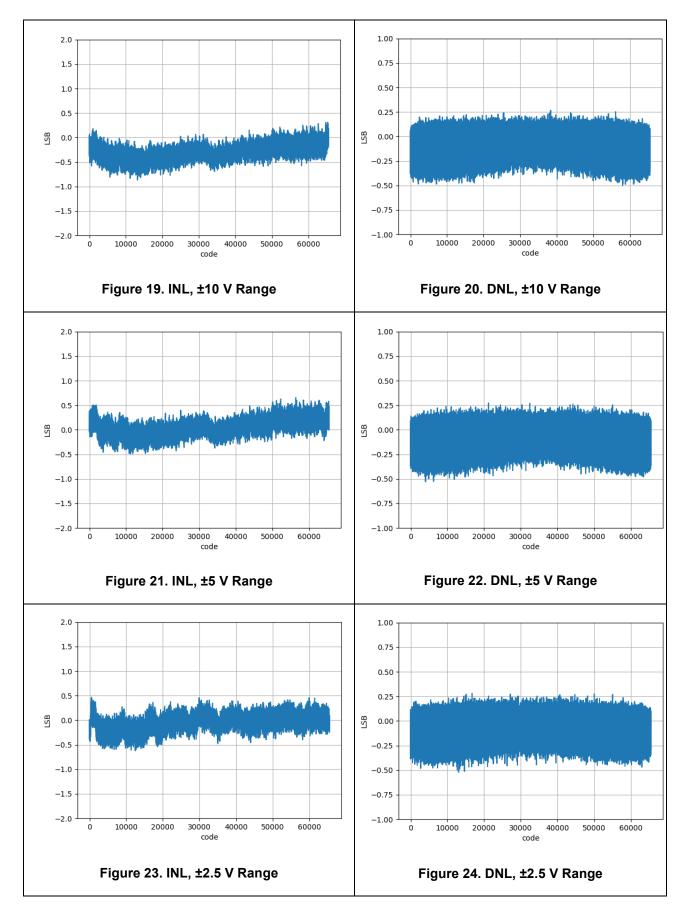

|    | 5.6          | GD30AD3380-I10 Typical Characteristics   |    |

| c  | 5.7<br>Euro  | GD30AD3380-I05 Typical Characteristics   |    |

| 6  |              | •                                        |    |

|    | 6.1          | Module Block Diagram                     |    |

| 7  | 6.2          | Operation<br>al Filter                   |    |

| 7  | -            |                                          |    |

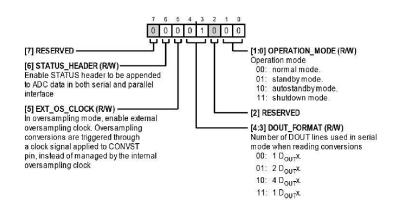

|    | 7.1          | Fill Oversampling.                       |    |

| 8  | 7.2<br>Svete | External Oversampling Clock              |    |

| 0  | -            | System Phase Calibration                 |    |

|    | 8.1<br>8.2   | System Gain Calibration                  |    |

|    | o.∠<br>8.3   | System Offset Calibration                |    |

|    | o.s<br>8.4   | Analog Input Open Circuit Detection      |    |

| 9  |              | al Interface                             | 44 |

| 5  | 9.1          | Hardware Mode                            |    |

|    | 9.2          | Software Mode                            |    |

|    | 9.3          | Parallel Interface                       |    |

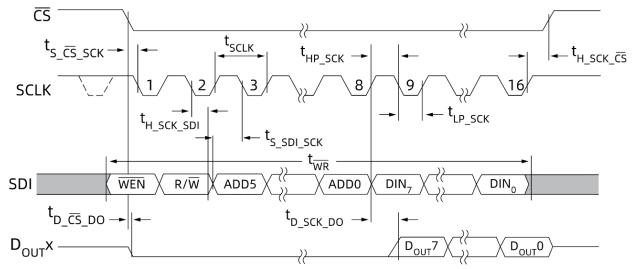

|    | 9.4          | Serial Interface                         |    |

| 10 |              | Iosis                                    |    |

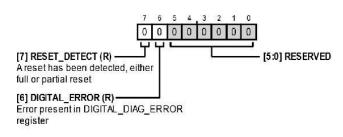

|    | 10.1         | Reset detection                          |    |

|    | 10.1         | Interface CRC Checksum                   |    |

|    | 10.3         | Diagnostic Multiplexer                   |    |

| 11 |              | al connection diagram                    |    |

| 12 |              | cation Information                       |    |

|    | 12.1         | Layout Guidelines                        |    |

| 13 | Regis        | ster Summary                             |    |

| 14 | •            | ster Details                             |    |

| 15 |              | aging information                        |    |

|    | 15.1         | Dimensions                               | 89 |

| 16 | Orde         | ring Information                         | 91 |

| 17 | Revis        | sion History                             | 92 |

# 4 Device Overview

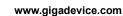

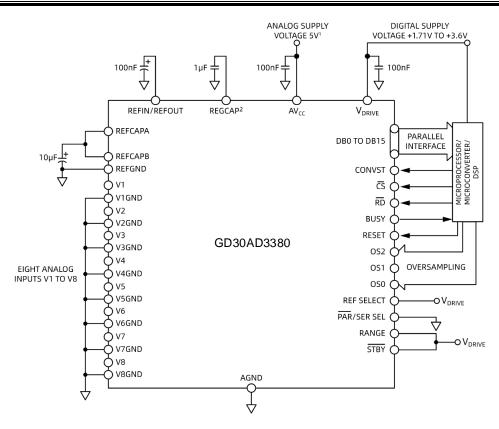

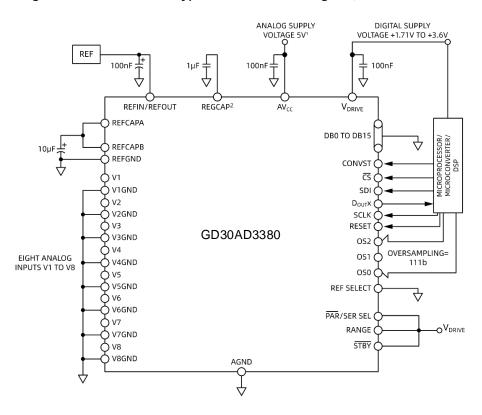

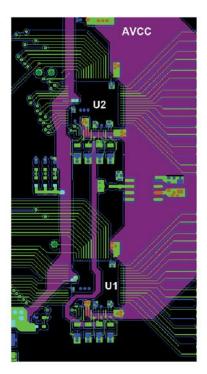

### 4.1 Pinout and Pin Assignment

# 4.2 Pin Description

| PIN         | IS                       | TYPE <sup>1</sup> | EUNCTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------------|--------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME        | NUM                      | ITPE              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| AVCC        | 1, 37, 38, 48            | Р                 | Analog supply voltage, 4.75 V to 5.25 V.<br>This is the supply voltage for the internal front-end amplifier and ADC core. Decouple these supply pins to AGND.                                                                                                                                                                                                                                   |  |  |  |

| AGND        | 2, 26, 35, 40,<br>41, 47 | Р                 | Analog ground.<br>These pins are the ground reference points for all analog circuits on<br>the GD30AD3380. All analog input signals and external reference<br>signals must be referenced to these pins. All six AGND pins must be<br>connected to the system's AGND plane.                                                                                                                      |  |  |  |

| OS0 to OS2  | 3 to 5                   | DI                | Oversampling mode pin.<br>These inputs select the oversampling rate or enable software mode<br>(see Table 4 for oversampling pin decoding). See the <i>Digital Filter</i><br>section for more information on the oversampling modes of operation.                                                                                                                                               |  |  |  |

| PAR/SER SEL | 6                        | DI                | Parallel/Serial Interface Select Input.<br>If this pin is tied to a logic low, the parallel interface is selected. If this<br>pin is tied to a logic high, the serial interface is selected. See the <i>Digital</i><br><i>Interface</i> section for more information on each available interface.                                                                                               |  |  |  |

| STBY        | 7                        | DI                | Standby mode input.<br>In hardware mode, this pin, together with the RANGE pin, places the GD30AD3380 into one of two power-saving modes: standby mode or shutdown mode. In software mode, this pin is ignored. Therefore, it is recommended to connect this pin to a logic high level. For more information on hardware mode and software mode, see the <i>Power-Saving Mode</i> section.      |  |  |  |

| RANGE       | 8                        | DI                | Analog Input Range Select Input.<br>In hardware mode, this pin determines the input range of the analog<br>input channel (see Table 1). If the STBY pin is at logic low, this pin<br>determines the power-saving mode (see Table 6). In software mode,<br>the RANGE pin is ignored. However, this pin must be tied high or low.                                                                 |  |  |  |

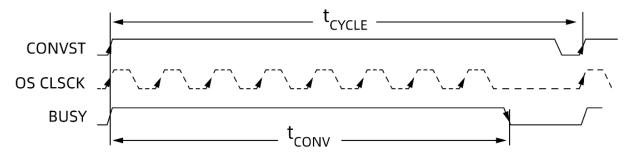

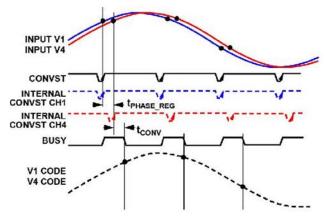

| CONVST      | 9                        | DI                | Conversion start input.<br>When the CONVST pin transitions from low to high, the analog inputs<br>are sampled on all eight SAR ADCs. In software mode, this pin can be<br>configured as an external oversampling clock. Providing a low jitter<br>external clock improves SNR performance at large oversampling<br>ratios. See the <i>External Oversampling Clock</i> section for more details. |  |  |  |

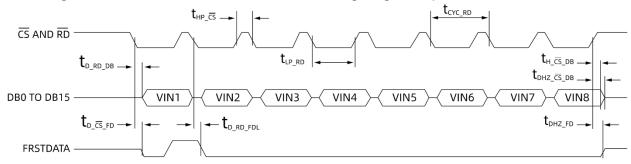

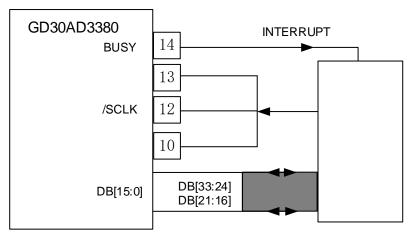

| WR          | 10                       | DI                | Digital input.<br>In GD30AD3380-I10 hardware mode, this pin has no function.<br>Therefore, it can be tied high, low, or shorted to CONVST. In<br>GD30AD3380-I10 software mode, this pin is an active low write pin<br>used to write registers through the parallel interface. For more<br>information, see the <i>Parallel Interface</i> section.                                               |  |  |  |

| RESET       | 11                       | DI                | Reset input, high level is valid.<br>Full reset and partial reset options are available. The type of reset is<br>determined by the length of the reset pulse. It is recommended that the<br>device receive a full reset pulse after power-up. See the Reset<br>Functionality section for details.                                                                                               |  |  |  |

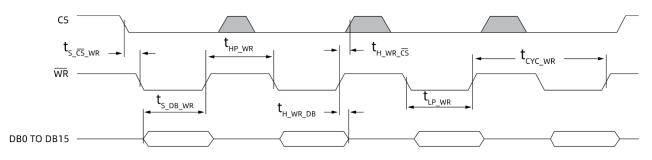

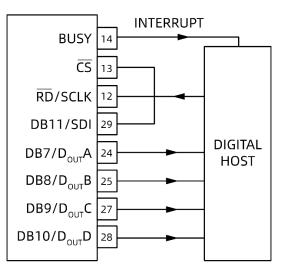

| RD/SCLK     | 12                       | DI                | Parallel data read control input (RD) when the parallel interface is selected.<br>Serial clock input (SCLK) when a serial interface is selected. See the <i>Digital Interface</i> section for more information.                                                                                                                                                                                 |  |  |  |

| cs          | 13                       | DI                | Chip select.<br>For both the serial and parallel interfaces, this pin is an active low chip<br>select input for ADC data reading or register data reading and writing.<br>See the Digital Interface section for more information.                                                                                                                                                               |  |  |  |

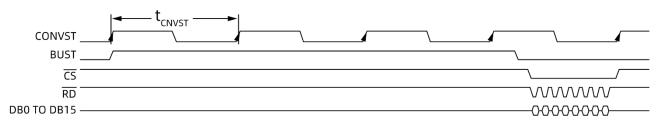

| BUSY        | 14                       | DO                | Output busy.<br>This pin goes logic high with the rising edge of CONVST. The BUSY<br>output remains high until the conversion process is complete for all<br>channels.                                                                                                                                                                                                                          |  |  |  |

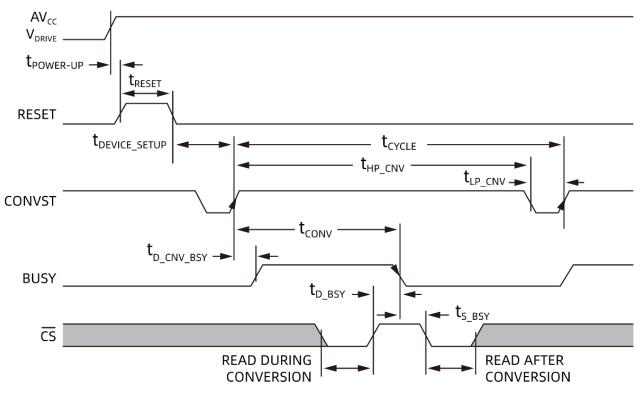

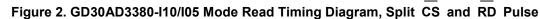

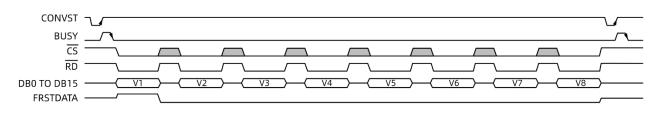

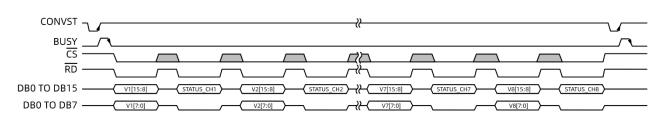

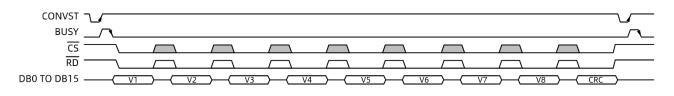

| FRSTDATA    | 15                       | DO                | First data output.<br>The FRSTDATA output signal indicates when the first channel, V1, is<br>being read back on the parallel interface (see Figure 2) or the serial<br>interface (see Figure 5). See the Digital Interface section for more<br>information.                                                                                                                                     |  |  |  |

| PIN                     | IS           |                   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-------------------------|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                    | NUM          | TYPE <sup>1</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DB0 to DB6              | 16 to 22     | DO/DI             | Parallel output/input data bits.<br>When using the parallel interface, these pins act as three-state parallel<br>digital input and output pins (see the <i>Parallel Interface</i> section). When<br>using the serial interface, these pins should be connected to AGND.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| VDRIVE                  | twenty three | Ρ                 | Logic Power Input.<br>The supply voltage at this pin (1.71 V to 3.6 V) determines the operating voltage of the logic interface. The nominal supply at this pin is the same as the supply for the host interface, that is, the digital signal processing (DSP) and field programmable gate array (FPGA).                                                                                                                                                                                                                                                                                                                 |  |  |  |

| DB7/DoutA               | twenty four  | DO/DI             | Parallel Output/Input Data Bit 7 (DB7)/Serial Interface Data Output Pin (D <sub>OUT</sub> A).<br>When using the parallel interface, this pin functions as a three-state parallel digital input/output pin. When using the serial interface, this pin functions as D <sub>OUT</sub> A. See Table 13 and Table 14.                                                                                                                                                                                                                                                                                                        |  |  |  |

| DB8/D <sub>OUT</sub> B  | 25           | DO/DI             | Parallel Output/Input Data Bit 8 (DB8)/Serial Interface Data Output Pin (D <sub>OUT</sub> B).<br>When using the parallel interface, this pin functions as a three-state parallel digital input/output pin. When using the serial interface, this pin functions as D <sub>OUT</sub> B. See Table 13 and Table 14.                                                                                                                                                                                                                                                                                                        |  |  |  |

| DB9/DoutC               | 27           | DO/DI             | Parallel Output/Input Data Bit 9 (DB9)/Serial Interface Data Output Pin ( $D_{OUT}C$ ).<br>When using the parallel interface, this pin functions as a three-state parallel digital input/output pin. When using the serial interface, if in software mode and using the four data output lines option, this pin functions as $D_{OUT}C$ . See Table 13 and Table 14.                                                                                                                                                                                                                                                    |  |  |  |

| DB10/D <sub>OUT</sub> D | 28           | DO/DI             | Parallel Output/Input Data Bit 10 (DB10)/Serial Interface Data Output Pin ( $D_{OUT}D$ ).<br>When using the parallel interface, this pin functions as a three-state parallel digital input/output pin. When using the serial interface, if in software mode and using the four data output lines option, this pin functions as $D_{OUT}D$ . See Table 13 and Table 14.                                                                                                                                                                                                                                                  |  |  |  |

| DB11/SDI                | 29           | DO/DI             | Parallel output/input data bit DB11/serial data input.<br>When using the parallel interface, this pin functions as a three-state<br>parallel digital input/output pin. When using the serial interface in<br>software mode, this pin functions as a serial data input. For more<br>information on the operating modes, see Table 13 and Table 14.                                                                                                                                                                                                                                                                       |  |  |  |

| DB12 to DB15            | 30 to 33     | DO/DI             | Parallel output/input data bits DB15 to DB12.<br>When using the parallel interface, these pins act as three-state parallel<br>digital input and output pins (see the <i>Parallel Interface</i> section). When<br>using the serial interface, these pins should be connected to AGND.                                                                                                                                                                                                                                                                                                                                    |  |  |  |

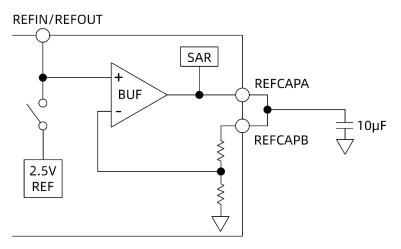

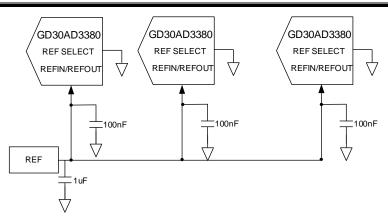

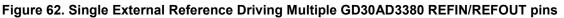

| REF SELECT              | 34           | DI                | Internal/external reference voltage selection logic input.<br>If this pin is set to logic high, the internal reference mode is selected<br>and enabled. If this pin is set to logic low, the internal reference is<br>disabled and an external reference must be applied to the<br>REFIN/REFOUT pin.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| REGCAP                  | 36, 39       | Р                 | Decoupling capacitor pin,<br>Voltage outputs for the 1.9 V internal regulator, the analog low dropout<br>(ALDO), and the digital low dropout (DLDO) regulators. These output<br>pins must be individually decoupled to AGND using 1 µF capacitors.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| REFIN/<br>REFOUT        | 42           | REF               | Reference voltage input (REFIN)/reference voltage output (REFOUT).<br>The internal 2.5 V reference can be made available for external use<br>through the REFOUT pin while setting the REF SELECT pin to logic<br>high. Alternatively, the internal reference can be disabled by setting the<br>REF SELECT pin to logic low, in which case an external 2.5 V reference<br>must be applied to this input (REFIN). For both the internal and external<br>reference options, a 100 nF capacitor must be applied from the REFIN<br>pin to ground (close to the REFGND pin). See the <i>Reference</i> section<br>for details. |  |  |  |

| REFGND                  | 43, 46       | REF               | Reference Voltage Ground Pin.<br>These pins must be connected to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| REFCAPA,<br>REFCAPB     | 44, 45       | REF               | Reference Voltage Buffered Output Force/Sense Pin.<br>These pins must be tied together and decoupled to AGND via low ESR (effective series resistance), 10 $\mu$ F ceramic capacitors. The voltage on these pins is typically 4.4 V.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

www.gigadevice.com

# GD30AD3380

| PIN   | IS  |                   |                                      |  |

|-------|-----|-------------------|--------------------------------------|--|

| NAME  | NUM | TYPE <sup>1</sup> | FUNCTION                             |  |

| V1    | 49  | AI                | Channel 1 Positive Analog Input Pin. |  |

| V1GND | 50  | AI GND            | Channel 1 negative analog input pin. |  |

| V2    | 51  | AI                | Channel 2 Positive Analog Input Pin. |  |

| V2GND | 52  | AI GND            | Channel 2 Negative Analog Input Pin. |  |

| V3    | 53  | AI                | Channel 3 Positive Analog Input Pin. |  |

| V3GND | 54  | AI GND            | Channel 3 Negative Analog Input Pin. |  |

| V4    | 55  | AI                | Channel 4 Positive Analog Input Pin. |  |

| V4GND | 56  | AI GND            | Channel 4 Negative Analog Input Pin. |  |

| V5    | 57  | AI                | Channel 5 Positive Analog Input Pin. |  |

| V5GND | 58  | AI GND            | Channel 5 Negative Analog Input Pin. |  |

| V6    | 59  | AI                | Channel 6 Positive Analog Input Pin. |  |

| V6GND | 60  | AI GND            | Channel 6 Negative Analog Input Pin. |  |

| V7    | 61  | AI                | Channel 7 Positive Analog Input Pin. |  |

| V7GND | 62  | AI GND            | Channel 7 Negative Analog Input Pin. |  |

| V8    | 63  | AI                | Channel 8 Positive Analog Input Pin. |  |

| V8GND | 64  | AI GND            | Channel 8 Negative Analog Input Pin. |  |

1. P stands for power supply, DI stands for digital input, DO stands for digital output, REF stands for reference voltage input / output, AI stands for analog input, and GND stands for ground.

# 5 Parameter information

# 5.1 Absolute Maximum Ratings

| PARAMETER                                    | RATING                   |

|----------------------------------------------|--------------------------|

| AV <sub>CC</sub> to AGND                     | -0.3 V to +7 V           |

| V <sub>DRIVE</sub> to AGND                   | -0.3 V to AVCC + 0.3 V   |

| Analog input voltage to AGND <sup>1</sup>    | ±25 V                    |

| Digital input voltage to AGND                | -0.3 V to VDRIVE + 0.3 V |

| Digital output voltage to AGND               | -0.3 V to VDRIVE + 0.3 V |

| REFIN to AGND                                | -0.3 V to AVCC + 0.3 V   |

| out current into any pin except supply pins1 | ±10 mA                   |

| Operating temperature range                  | -40°C to +125°C          |

| Storage temperature range                    | −65°C to +150°C          |

| Junction temperature                         | 150°C                    |

| Lead-tin soldering temperature               |                          |

| Reflow (10 seconds to 30 seconds)            | 240 (+0)°C               |

| Lead-free reflow temperature                 | 260 (+0)°C               |

| Electrostatic Discharge (ESD)                |                          |

| All pins except analog input                 | 3.5 kV                   |

| Analog input pins only                       | 7 kV                     |

1. Transient currents below 100 mA will not cause silicon-controlled rectifier (SCR) latch-up.

2. Note that exposure to conditions equal to or exceeding the absolute maximum ratings listed above may cause permanent damage to the product. These are maximum ratings only and do not imply that the device will operate normally under these conditions or any other conditions beyond those shown in the operational section of this technical specification. Extended exposure to conditions exceeding the maximum ratings may affect product reliability.

# 5.2 Thermal resistance

Thermal performance is directly related to the printed circuit board (PCB) design and the operating environment. PCB heat dissipation design must be treated with caution.

$\theta_{JA}$  is the junction-to-ambient thermal resistance under natural convection, measured in a 1 cubic foot sealed enclosure.  $\theta_{JC}$  is the junction-to-case thermal resistance.

| PACKAGE TYPE | θ <sub>JA</sub> 1 | θ <sub>JC</sub> 1 | UNIT |

|--------------|-------------------|-------------------|------|

| LQFP-64      | 40                | 7                 | °C/W |

1. Simulation data based on JEDEC 2S2P thermal test PCB in JEDEC natural convection environment.

### 5.3 GD30AD3380-I10 Electrical Characteristic

Unless otherwise noted, reference voltage ( $V_{REF}$ ) = 2.5 V internal reference, analog supply voltage ( $AV_{CC}$ ) = 4.75 V to 5.25 V, logic supply voltage ( $V_{DRIVE}$ ) = 1.71 V to 3.6 V, sampling frequency ( $f_{SAMPLE}$ ) = 1 MSPS, no oversampling,  $T_A$  = -40 °C to +125 °C, single-ended input, all input voltage ranges.

| PARAMETER                                                      | TEST CONDITIONS/COMMENTS                                                    | MIN | ТҮР  | MAX | UNIT |

|----------------------------------------------------------------|-----------------------------------------------------------------------------|-----|------|-----|------|

| Dynamic performance                                            | Input frequency (f <sub>IN</sub> ) = 1 kHz sine wave unless otherwise noted |     |      |     |      |

| Signal-to-Noise Ratio (SNR) <sup>1</sup><br>Low Bandwidth Mode | No OS, ±12.5 V range                                                        | 87  | 90   |     | dB   |

|                                                                | No OS, ±10 V range                                                          | 87  | 90   |     | dB   |

|                                                                | No OS, ±5 V range                                                           | 86  | 88.5 |     | dB   |

Unless otherwise noted, reference voltage (V<sub>REF</sub>) = 2.5 V internal reference, analog supply voltage (AV<sub>CC</sub>) = 4.75 V to 5.25 V, logic supply voltage (V<sub>DRIVE</sub>) = 1.71 V to 3.6 V, sampling frequency (f<sub>SAMPLE</sub>) = 1 MSPS, no oversampling, T<sub>A</sub> = -40 °C to +125 °C, single-ended input, all input voltage ranges.

|                                                                 | TEST CONDITIONS/COMMENTS                                                          | MIN | TYP  | MAX   | UNIT |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|------|-------|------|

|                                                                 |                                                                                   |     |      | IVIAA |      |

|                                                                 | No OS, ±2.5 V range                                                               | 83  | 86   |       | dB   |

|                                                                 | OSR = 16×,±12.5 V range                                                           | 93  | 96   |       | dB   |

|                                                                 | OSR = 16×,±10 V range                                                             | 92  | 95.5 |       | dB   |

|                                                                 | OSR = 16×, ±5 V range                                                             | 91  | 94   |       | dB   |

|                                                                 | OSR = 16×, ±2.5 V range                                                           | 89  | 92   |       | dB   |

| Signal-to-Noise Ratio (SNR)<br><sup>1</sup> High Bandwidth Mode | No OS,±12.5 V range                                                               |     | 87.5 |       | dB   |

|                                                                 | No OS,±10 V range                                                                 |     | 88   |       | dB   |

|                                                                 | No OS,±5 V range                                                                  |     | 84   |       | dB   |

|                                                                 | No OS,±2.5 V range                                                                |     | 81.5 |       | dB   |

| Total Harmonic Distortion<br>(THD)Low bandwidth mode            | All input ranges                                                                  |     | -103 | -94   | dB   |

| SNRLow bandwidth mode                                           | No OS,±12.5 V range                                                               | 87  | 90   |       | dB   |

|                                                                 | No OS,±10 V range                                                                 | 87  | 90   |       | dB   |

|                                                                 | No OS,±5 V range                                                                  | 86  | 89   |       | dB   |

|                                                                 | No OS,±2.5 V range                                                                | 83  | 86   |       | dB   |

|                                                                 | OSR = 16×, ±12.5 V range     92     95       OSR = 16×, ±10 V range     91     94 | dB  |      |       |      |

|                                                                 | OSR = 16×,±10 V range                                                             | 91  | 94   |       | dB   |

|                                                                 | OSR = 16×,±5 V range                                                              | 90  | 93.5 |       | dB   |

|                                                                 | OSR = 16×,±2.5 V range                                                            | 88  | 91.5 |       | dB   |

| SNRHigh Bandwidth Mode                                          | No OS,±12.5 V range                                                               |     | 87   |       | dB   |

|                                                                 | No OS,±10 V range                                                                 |     | 87   |       | dB   |

|                                                                 | No OS,±5 V range                                                                  |     | 83   |       | dB   |

|                                                                 | No OS,±2.5 V range                                                                |     | 81   |       | dB   |

| Spurious Free Dynamic<br>Range (SFDR)                           |                                                                                   |     | -104 |       | dB   |

|                                                                 | f <sub>IN</sub> up to 160 kHz for unselected channels                             |     | -110 |       | dB   |

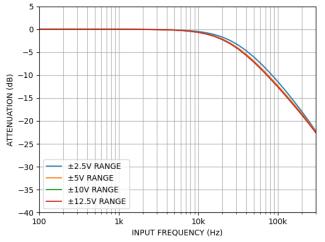

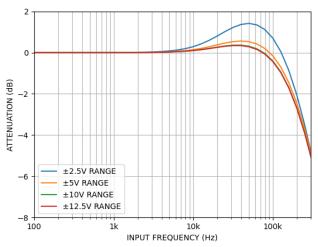

| Analog Input Filter                                             |                                                                                   |     |      |       |      |

| Full Power BandwidthLow<br>Bandwidth Mode                       | -3 dB                                                                             |     | 25   |       | kHz  |

|                                                                 | -0.1 dB                                                                           |     | 3.9  |       | kHz  |

| Full Power BandwidthHigh<br>Bandwidth Mode                      | -3 dB                                                                             |     | 200  |       | kHz  |

|                                                                 | -0.1 dB                                                                           |     | 25   |       | kHz  |

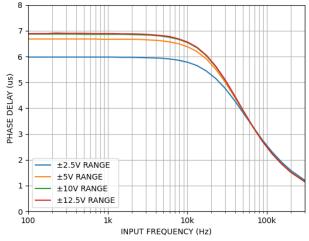

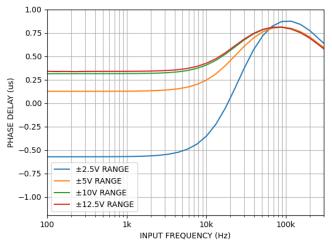

| Phase DelayLow<br>Bandwidth Mode                                | ±12.5 V, ±10 V range                                                              |     | 6.9  |       | μs   |

|                                                                 | ±5 V range                                                                        |     | 6.7  |       | μs   |

|                                                                 | ±2.5 V range                                                                      |     | 6    |       | μs   |

Unless otherwise noted, reference voltage (V<sub>REF</sub>) = 2.5 V internal reference, analog supply voltage (AV<sub>CC</sub>) = 4.75 V to 5.25 V, logic supply voltage (V<sub>DRIVE</sub>) = 1.71 V to 3.6 V, sampling frequency (f<sub>SAMPLE</sub>) = 1 MSPS, no oversampling, T<sub>A</sub> = -40 °C to +125 °C, single-ended input, all input voltage ranges.

| PARAMETER                                                | TEST CONDITIONS/COMMENTS                 | MIN   | ТҮР  | MAX   | UNIT             |

|----------------------------------------------------------|------------------------------------------|-------|------|-------|------------------|

| Phase DelayHigh<br>Bandwidth Mode                        | ±12.5 V, ±10 V range                     |       | 0.3  |       | μs               |

|                                                          | ±5 V range                               |       | 0.1  |       | μs               |

|                                                          | ±2.5 V range                             |       | -0.6 |       | μs               |

| Phase Delay Matching – Low Bandwidth Mode                |                                          |       |      | 200   | ns               |

| Phase Delay Matching –<br>High Bandwidth Mode            |                                          |       |      | 30    | ns               |

| DC accuracy                                              |                                          |       |      |       |                  |

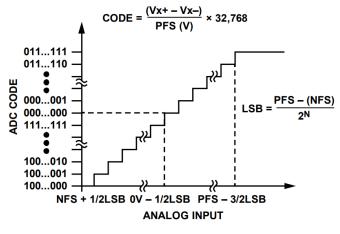

| Resolution                                               | No missing codes                         | 16    |      |       | 位                |

| Differential Nonlinearity<br>(DNL)                       |                                          |       | ±0.6 | ±0.99 | LSB <sup>2</sup> |

| Integral Nonlinearity (INL)                              | f <sub>SAMPLE</sub> = 1 MSPS             |       | ±1   | ±2.5  | LSB <sup>2</sup> |

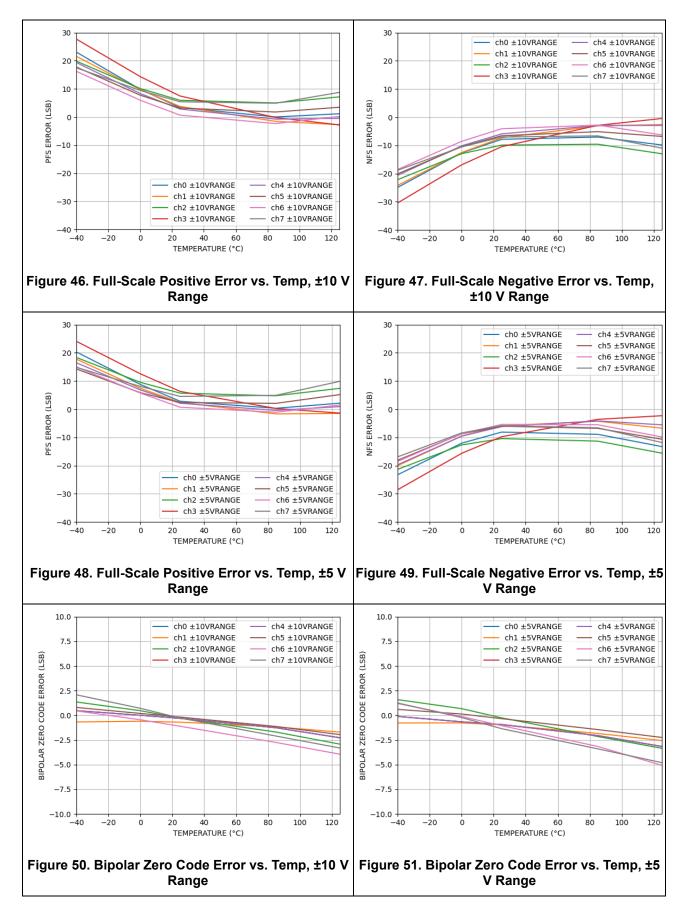

| • • • • •                                                | Internal voltage reference               |       | ±16  |       | LSB              |

| Positive and negative full scale (FS) error <sup>3</sup> | External voltage reference               |       | ±8   | ±50   | LSB              |

|                                                          | Internal voltage reference               |       | ±8   |       | LSB              |

| Positive and negative full scale (FS) error drift        | External voltage reference               |       | ±4   |       | ppm/°C           |

|                                                          | Internal voltage reference               |       | ±8   |       | ppm/°C           |

| Positive and negative FS error matching                  |                                          |       | 12   | 60    | LSB              |

| Bipolar Zero Code Error                                  |                                          |       | ±3   | ±12   | LSB <sup>2</sup> |

| Bipolar Zero Code Error Drift                            |                                          |       | ±0.6 | ±2    | ppm/°C           |

| Bipolar Zero Code Error<br>Matching                      |                                          |       | 6    | 24    | LSB <sup>2</sup> |

| Analog Input                                             |                                          |       |      |       |                  |

| Input voltage range                                      | Vx – VxGND                               |       |      |       |                  |

|                                                          | ±12.5 V range                            | -12.5 |      | +12.5 | V                |

|                                                          | ±10 V range                              | -10   |      | +10   | V                |

|                                                          | ±5 V range                               | -5    |      | +5    | V                |

|                                                          | ±2.5 V range                             | -2.5  |      | +2.5  | V                |

| Input voltage range                                      | VxGND – AGND                             |       |      |       |                  |

|                                                          | ±12.5 V range                            | -1    |      | +1.6  | V                |

|                                                          | ±10 V range                              | -0.7  |      | +1.9  | V                |

|                                                          | ±5 V range                               | -0.1  |      | +2.7  | V                |

|                                                          | ±2.5 V range                             | -0.1  |      | +3.1  | V                |

| Analog input current                                     |                                          |       | 8    |       | μA               |

| Input Capacitor(C) <sup>4</sup>                          |                                          |       | 5    |       | pF               |

| Input impedance (R) <sup>5</sup>                         |                                          | 1     |      |       | MΩ               |

| Reference voltage<br>input/output                        |                                          |       |      |       |                  |

| Reference input voltage                                  | REF SELECT=0, External voltage reference | 2.475 | 2.5  | 2.525 | V                |

Unless otherwise noted, reference voltage (V<sub>REF</sub>) = 2.5 V internal reference, analog supply voltage (AV<sub>CC</sub>) = 4.75 V to 5.25 V, logic supply voltage (V<sub>DRIVE</sub>) = 1.71 V to 3.6 V, sampling frequency (f<sub>SAMPLE</sub>) = 1 MSPS, no oversampling, T<sub>A</sub> = -40 °C to +125 °C, single-ended input, all input voltage ranges.

| PARAMETER                                   | TEST CONDITIONS/COMMENTS                                      | MIN                     | TYP   | MAX                    | UNIT             |

|---------------------------------------------|---------------------------------------------------------------|-------------------------|-------|------------------------|------------------|

| DC leakage current                          |                                                               |                         |       | ±0.1                   | μA               |

| Input Capacitor <sup>4</sup>                |                                                               |                         | 7.5   |                        | pF               |

| Reference output voltage                    | REF SELECT=1, Internal voltage reference, $T_A = 25^{\circ}C$ | 2.495                   | 2.5   | 2.505                  | V                |

| Reference source<br>temperature coefficient |                                                               |                         | ±10   |                        | ppm/°C           |

| ADC reference voltage                       | REFCAPA(PIN 44)和 REFCAPB(PIN<br>45)                           | 4.086                   | 4.096 | 4.106                  | V                |

| Logic Input                                 |                                                               |                         |       |                        |                  |

| Input High Voltage (V <sub>INH</sub> )      |                                                               | 0.7×V <sub>DRIVE</sub>  |       |                        | V                |

| Input Low Voltage (VINL)                    |                                                               |                         |       | 0.3×V <sub>DRIVE</sub> | V                |

| Input Current (I <sub>IN</sub> )            |                                                               |                         |       | ±1                     | μA               |

| Input Capacitor <sup>4</sup>                |                                                               |                         | 5     |                        | pF               |

| Logic Output                                |                                                               |                         |       |                        |                  |

| Output high voltage (Vон )                  | Source current (I <sub>SOURCE</sub> ) = 100 μA                | V <sub>DRIVE</sub> -0.2 |       |                        | V                |

| Output low voltage (V <sub>OL</sub> )       | Sink current (I <sub>SINK</sub> ) = 100 μA                    |                         |       | 0.2                    | V                |

| Floating state leakage<br>current           |                                                               |                         | ±1    | ±20                    | μA               |

| Output capacitor <sup>6</sup>               |                                                               |                         | 5     |                        | pF               |

| Output Encoding                             | Two's complement                                              |                         |       |                        | N/A <sup>6</sup> |

| Conversion rate                             |                                                               |                         |       |                        |                  |

| Conversion time                             |                                                               |                         | 0.54  |                        | μs               |

| Collection time                             |                                                               |                         | 0.46  |                        | μs               |

| Throughput rate                             | Per channel                                                   |                         |       | 1                      | MSPS             |

| Power Requirements                          |                                                               |                         |       |                        |                  |

| AVcc                                        |                                                               | 4.75                    | 5     | 5.25                   | V                |

| V <sub>DRIVE</sub>                          |                                                               | 1.71                    | 3.3   | 3.6                    | V                |

| REGCAP                                      |                                                               | 1.875                   |       | 1.93                   | V                |

| AVcc Current (Iavcc )                       |                                                               |                         |       |                        |                  |

| Normal mode (static)                        |                                                               |                         | 10.6  |                        | mA               |

| Normal mode (working state)                 | f <sub>SAMPLE</sub> = 1 MSPS                                  |                         | 25.5  |                        | mA               |

|                                             | f <sub>SAMPLE</sub> = 10 KSPS                                 |                         | 11.4  |                        | mA               |

| Standby                                     |                                                               |                         | 7.2   |                        | mA               |

| Shutdown Mode                               |                                                               |                         | 0.6   |                        | μA               |

| Idrive                                      |                                                               |                         |       |                        |                  |

| Normal mode (static)                        |                                                               |                         | 0.2   |                        | μA               |

| Normal mode (working state)                 | f <sub>SAMPLE</sub> = 1 MSPS                                  |                         | 1.6   |                        | mA               |

|                                             | f <sub>SAMPLE</sub> = 10 KSPS                                 |                         | 30    |                        | μA               |

| Standby                                     |                                                               |                         | 0.16  |                        | μA               |

Unless otherwise noted, reference voltage ( $V_{REF}$ ) = 2.5 V internal reference, analog supply voltage ( $AV_{CC}$ ) = 4.75 V to 5.25 V, logic supply voltage ( $V_{DRIVE}$ ) = 1.71 V to 3.6 V, sampling frequency ( $f_{SAMPLE}$ ) = 1 MSPS, no oversampling,  $T_A$  = -40 °C to +125 °C, single-ended input, all input voltage ranges.

| PARAMETER                   | TEST CONDITIONS/COMMENTS      | MIN | ТҮР | MAX | UNIT |

|-----------------------------|-------------------------------|-----|-----|-----|------|

| Shutdown Mode               |                               |     | 0.1 |     | μA   |

| Power consumption           |                               |     |     |     |      |

| Normal mode (static)        |                               |     | 53  |     | mW   |

| Normal mode (working state) | f <sub>SAMPLE</sub> = 1 MSPS  |     | 133 |     | mW   |

|                             | f <sub>SAMPLE</sub> = 10 KSPS |     | 57  |     | mW   |

| Standby                     |                               |     | 36  |     | mW   |

| Shutdown Mode               |                               |     | 3.5 |     | μW   |

1. No OS means no oversampling is applied.

LSB stands for least significant bit. For ±2.5 V input range, 1 LSB = 76.293 μV. For ±5 V input range, 1 LSB = 152.58 μV. For ±10 V input range, 1 LSB = 305.175 μV.

3. These specifications include full temperature variation as well as the contribution from the internal reference and reference buffer.

4. Not production tested. Samples are tested during initial release to ensure compliance with standards.

5. N/A means not applicable.

### 5.4 GD30AD3380-I05 Electrical Characteristic

Unless otherwise noted, reference voltage ( $V_{REF}$ ) = 2.5 V internal reference, analog supply voltage ( $AV_{CC}$ ) = 4.75 V to 5.25V, logic supply voltage ( $V_{DRIVE}$ ) = 1.71 V to 5 V, sampling frequency ( $f_{SAMPLE}$ ) = 500 KSPS, no oversampling,  $T_A$  = -40 °C to +125 °C, single-ended input, all input voltage ranges.

| PARAMETER                                                      | TEST CONDITIONS/COMMENTS                                                    | MIN | TYP  | MAX | UNIT |

|----------------------------------------------------------------|-----------------------------------------------------------------------------|-----|------|-----|------|

| Dynamic performance                                            | Input frequency $(f_{IN}) = 1 \text{ kHz}$ sine wave unless otherwise noted |     |      |     |      |

| Signal-to-Noise Ratio (SNR) <sup>1</sup><br>Low Bandwidth Mode | No OS,±10 V range                                                           | 87  | 90   |     | dB   |

|                                                                | No OS,±5 V range                                                            | 86  | 89   |     | dB   |

|                                                                | OSR = 16×,±10 V range                                                       | 92  | 95.5 |     | dB   |

|                                                                | OSR = 16×,±5 V range                                                        | 91  | 94   |     | dB   |

| Total Harmonic Distortion<br>(THD)                             |                                                                             |     | -103 | -94 | dB   |

| Signal-to-Noise Ratio (SNR)                                    | No OS,±12.5 V range                                                         | 87  | 90   |     | dB   |

|                                                                | No OS,±10 V range                                                           | 87  | 90   |     | dB   |

| Spurious Free Dynamic<br>Range (SFDR)                          |                                                                             |     | -104 |     | dB   |

| Channel-to-channel isolation                                   | $f_{IN}$ up to 20 kHz for unselected channels                               |     | -110 |     | dB   |

| Analog Input Filter                                            |                                                                             |     |      |     |      |

| Full Power BandwidthLow<br>Bandwidth Mode                      | −3 dB, ±10 V range                                                          |     | 25   |     | kHz  |

|                                                                | −3 dB, ±5 V range                                                           |     | 25   |     | kHz  |

|                                                                | −0.1 dB, ±10 V range                                                        |     | 3.9  |     | kHz  |

|                                                                | −0.1 dB, ±5 V range                                                         |     | 3.9  |     | kHz  |

| Phase Delay                                                    | ±10 V range                                                                 |     | 6.9  |     | μs   |

|                                                                | ±5 V range                                                                  |     | 6.7  |     | μs   |

| Phase Delay Matching                                           |                                                                             |     |      | 200 | ns   |

| DC accuracy                                                    |                                                                             |     |      |     |      |

Unless otherwise noted, reference voltage (V<sub>REF</sub>) = 2.5 V internal reference, analog supply voltage (AV<sub>CC</sub>) = 4.75 V to 5.25 V, logic supply voltage (V<sub>DRIVE</sub>) = 1.71 V to 5 V, sampling frequency ( $f_{SAMPLE}$ ) = 500 KSPS, no oversampling,  $T_A = -40$  °C to +125 °C, single-ended input, all input voltage ranges.

| PARAMETER                                                | TEST CONDITIONS/COMMENTS                        | MIN                    | TYP  | MAX   | UNIT             |

|----------------------------------------------------------|-------------------------------------------------|------------------------|------|-------|------------------|

| Resolution                                               | No missing codes                                | 16                     |      |       | 位                |

| Differential Nonlinearity<br>(DNL)                       |                                                 |                        | ±0.6 | ±0.99 | LSB <sup>2</sup> |

| Integral Nonlinearity (INL)                              | f <sub>SAMPLE</sub> = 1 MSPS                    |                        | ±1   | ±2.5  | LSB <sup>2</sup> |

| Total Unadjusted Error (TUE)                             | ±10V range                                      |                        | ±10  |       | LSB              |

|                                                          | ±5V range                                       |                        | ±16  |       | LSB              |

| Positive and negative full scale (FS) error <sup>3</sup> | External voltage reference                      |                        | ±8   | ±50   | LSB              |

|                                                          | Internal voltage reference                      |                        | ±8   |       | LSB              |

| Positive and negative full<br>scale (FS) error drift     | External voltage reference                      |                        | ±4   |       | ppm/°C           |

|                                                          | Internal voltage reference                      |                        | ±8   |       | ppm/°C           |

| Positive and negative FS<br>error matching               | ±10V range                                      |                        | 10   | 50    | LSB              |

|                                                          | ±5V range                                       |                        | 12   | 60    | LSB              |

| Bipolar Zero Code Error                                  | ±10V range                                      |                        | ±1   | ±6    | LSB <sup>2</sup> |

|                                                          | ±5V range                                       |                        | ±3   | ±12   | LSB              |

| Bipolar Zero Code Error Drift                            | ±10V range                                      |                        | 10   |       | µV/°C            |

| Bipolar Zero Code Error<br>Matching                      | ±10V range                                      |                        | 1    | 12    | LSB2             |

|                                                          | ±5V range                                       |                        | 6    | 24    | LSB              |

| Analog Input                                             |                                                 |                        |      |       |                  |

| Input voltage range                                      | Vx – VxGND                                      |                        |      |       |                  |

|                                                          | ±10 V range                                     | -10                    |      | +10   | V                |

|                                                          | ±5 V range                                      | -5                     |      | +5    | V                |

| Input voltage range                                      | VxGND – AGND                                    |                        |      |       |                  |

|                                                          | ±10 V range                                     | -0.7                   |      | +1.9  | V                |

|                                                          | ±5 V range                                      | -0.1                   |      | +2.7  | V                |

| Analog input current                                     |                                                 |                        | 8    |       | μA               |

| Input Capacitor(C) <sup>4</sup>                          |                                                 |                        | 5    |       | pF               |

| Input impedance (R) <sup>5</sup>                         |                                                 |                        | 1    |       | MΩ               |

| Reference voltage<br>input/output                        |                                                 |                        |      |       |                  |

| Reference input voltage                                  | REF SELECT=0, external reference voltage source | 2.475                  | 2.5  | 2.525 | V                |

| DC leakage current                                       |                                                 |                        |      | ±0.1  | μA               |

| Input Capacitor <sup>4</sup>                             |                                                 |                        | 7.5  |       | pF               |

| Reference output voltage                                 | REF SELECT=1, internal reference voltage source |                        | 2.5  |       | V                |

| Reference source<br>temperature coefficient              |                                                 |                        | ±10  |       | ppm/°C           |

| ADC reference voltage                                    |                                                 |                        |      |       |                  |

| Input High Voltage (V <sub>INH</sub> )                   |                                                 | 0.7×V <sub>DRIVE</sub> |      |       | V                |

Unless otherwise noted, reference voltage ( $V_{REF}$ ) = 2.5 V internal reference, analog supply voltage ( $AV_{CC}$ ) = 4.75 V to 5.25 V, logic supply voltage ( $V_{DRIVE}$ ) = 1.71 V to 5 V, sampling frequency ( $f_{SAMPLE}$ ) = 500 KSPS, no oversampling,  $T_A$  = -40 °C to +125 °C, single-ended input, all input voltage ranges.

| PARAMETER                             | TEST CONDITIONS/COMMENTS          | MIN                     | TYP  | MAX                    | UNIT |

|---------------------------------------|-----------------------------------|-------------------------|------|------------------------|------|

| Input Low Voltage (V <sub>INL</sub> ) |                                   |                         |      | 0.3×V <sub>DRIVE</sub> | V    |

| Input Current (I <sub>IN</sub> )      |                                   |                         |      | ±2                     | μA   |

| Input Capacitor <sup>4</sup>          |                                   |                         | 5    |                        | pF   |

| Logic Output                          |                                   |                         |      |                        |      |

| Output high voltage (Vон)             | Source current (ISOURCE) = 100 μA | V <sub>DRIVE</sub> -0.2 |      |                        | V    |

| Output low voltage (VoL)              | Sink current (ISINK) = 100 μA     |                         |      | 0.2                    | V    |

| Floating state leakage<br>current     |                                   |                         | ±1   | ±20                    | μA   |

| Output capacitor 6                    |                                   |                         | 5    |                        | pF   |

| Output Encoding                       | Two's complement                  |                         |      |                        | N/A5 |

| Conversion rate                       |                                   |                         |      |                        |      |

| Conversion time                       |                                   |                         | 1.0  |                        | μs   |

| Collection time                       |                                   |                         | 1.0  |                        | μs   |

| Throughput rate                       | Per channel                       |                         |      | 500                    | KSPS |

| Power Requirements                    |                                   |                         |      |                        |      |

| AVCC                                  |                                   | 4.75                    | 5    | 5.25                   | V    |

| VDRIVE                                |                                   | 1.71                    | 3.3  | 5.25                   | V    |

| AVcc Current (IAVcc )                 |                                   |                         |      |                        |      |

| Normal mode (static)                  |                                   |                         | 10   |                        | mA   |

| Normal mode (working state)           | f <sub>SAMPLE</sub> = 500 KSPS    |                         | 22   |                        | mA   |

| Standby                               |                                   |                         | 7.2  |                        | mA   |

| Shutdown Mode                         |                                   |                         | 0.6  |                        | μA   |

| DRIVE                                 |                                   |                         |      |                        |      |

| Normal mode (static)                  |                                   |                         | 30   |                        | μA   |

| Normal mode (working state)           | f <sub>SAMPLE</sub> = 500 KSPS    |                         | 1.7  |                        | mA   |

| Standby                               |                                   |                         | 0.16 |                        | μA   |

| Shutdown Mode                         |                                   |                         | 0.1  |                        | μA   |

| Power consumption                     |                                   |                         |      |                        |      |

| Normal mode (static)                  |                                   |                         | 50   |                        | mW   |

| Normal mode (working state)           | f <sub>SAMPLE</sub> = 500 KSPS    |                         | 116  |                        | mW   |

| Standby                               |                                   |                         | 36   |                        | mW   |

| Shutdown Mode                         |                                   |                         | 3.5  |                        | μW   |

1. No OS means no oversampling is applied.

2. LSB stands for least significant bit. For ±2.5 V input range, 1 LSB = 76.293 μV. For ±5 V input range, 1 LSB = 152.58 μV. For ±10 V input range, 1 LSB = 305.175 μV.

3. These specifications include full temperature variation as well as the contribution from the internal reference and reference buffer.

4. Not production tested. Samples are tested during initial release to ensure compliance with standards.

5. N/A means not applicable.

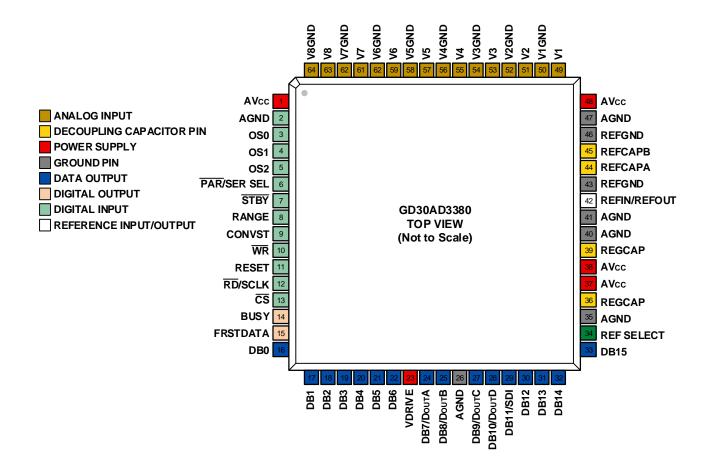

# 5.5 Timing Specifications

### 5.5.1 GD30AD3380-I10 General Timing Specifications

$AV_{CC}$  = 4.75 V to 5.25 V ,  $V_{DRIVE}$  = 1.71 V to 3.6 V ,  $V_{REF}$  = 2.5 V external reference and internal reference,  $T_A$  = -40°C to +125°C, unless otherwise noted . Interface timing is tested with 20 pF load capacitance and is dependent on  $V_{DRIVE}$  and the load capacitance of the serial interface.

| PARAMETER             | MIN   | ТҮР | MAX   | UNIT | DESCRIBE                                                                                                                                                                                             |

|-----------------------|-------|-----|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

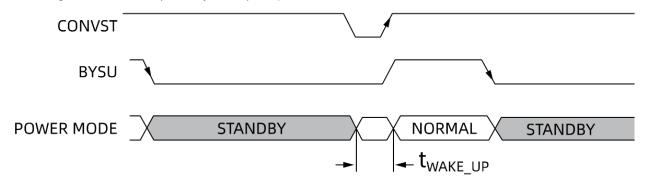

| tcycle                | 1     |     |       | μs   | Minimum time between consecutive CONVST rising edges (excluding oversampling mode) <sup>1</sup>                                                                                                      |

| tlp_cnv               | 80    |     |       | ns   | CONVST low level pulse width                                                                                                                                                                         |

| t <sub>HP_CNV</sub>   | 80    |     |       | ns   | CONVST high level pulse width                                                                                                                                                                        |

| td_cnv_bsy            |       |     |       |      | CONVST high level to BUSY high level delay time                                                                                                                                                      |

|                       |       |     | 20    | ns   | $V_{DRIVE} > 2.7 V$                                                                                                                                                                                  |

|                       |       |     | 25    | ns   | $V_{DRIVE} < 2.7 V$                                                                                                                                                                                  |

| ts_bsy                | 0     |     |       | ns   | From the BUSY falling edge to $\overline{RD}$ the falling edge<br>setup time (parallel interface) or to the D <sub>OUT</sub> X line<br>providing the MSB (serial interface)                          |

| td_bsy                |       |     | 25    | ns   | The last $\overline{\text{RD}}$ falling edge ( <i>Parallel Interface</i> ) or the last LSB being clocked out ( <i>Serial Interface</i> ) to the subsequent BUSY falling edge; read during conversion |

| tconv                 | 0.5   |     | 0.62  | μs   | Conversion time; no oversampling                                                                                                                                                                     |

|                       | 2.2   |     | 2.3   | μs   | 2x oversampling                                                                                                                                                                                      |

|                       | 4.65  |     | 4.8   | μs   | 4x oversampling                                                                                                                                                                                      |

|                       | 9.6   |     | 9.9   | μs   | 8x oversampling                                                                                                                                                                                      |

|                       | 19.4  |     | 20    | μs   | 16x oversampling                                                                                                                                                                                     |

|                       | 39.2  |     | 40.2  | μs   | 32x oversampling                                                                                                                                                                                     |

|                       | 78.7  |     | 80.8  | μs   | 64x oversampling                                                                                                                                                                                     |

|                       | 157.6 |     | 161.9 | μs   | 128 times oversampling                                                                                                                                                                               |

|                       | 315.6 |     | 324   | μs   | 256 times oversampling                                                                                                                                                                               |

| treset                |       |     |       |      |                                                                                                                                                                                                      |

| Partial Reset         | 55    |     | 2000  | ns   | Partial RESET high level pulse width                                                                                                                                                                 |

| Complete reset        | 3000  |     |       | ns   | Full RESET high level pulse width                                                                                                                                                                    |

| tdevice_setup         |       |     |       | μs   | Time between RESET falling edge and first CONVST rising edge                                                                                                                                         |

| Partial Reset         | 80    |     |       | ns   |                                                                                                                                                                                                      |

| Complete reset        | 600   |     |       | μs   |                                                                                                                                                                                                      |

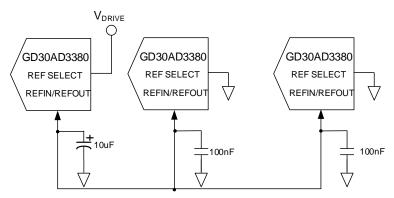

| twake-up              |       |     |       |      | Wake-up time after standby/shutdown mode                                                                                                                                                             |

| Standby               | 1     |     |       | μs   |                                                                                                                                                                                                      |

| Shutdown              | 10    |     |       | ms   |                                                                                                                                                                                                      |

| t <sub>POWER-UP</sub> | 10    |     |       | ms   | Time between stable $V_{CC}$ / $V_{DRIVE}$ and RESET assertion                                                                                                                                       |

1. Applicable in serial mode (when all four DOUTX lines are selected).

#### 5.5.2 GD30AD3380-I05 General Timing Specifications

$AV_{CC} = 4.75 V$  to 5.25 V,  $V_{DRIVE} = 1.71 V$  to 5 V,  $V_{REF} = 2.5 V$  external reference and internal reference,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted . Interface timing is tested with 20 pF load capacitance and is dependent on  $V_{DRIVE}$  and the load capacitance of the serial interface.

| PARAMETER           | MIN  | TYP | MAX  | UNIT | DESCRIBE                                                                                                                                                                                             |

|---------------------|------|-----|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tcycle              | 2    |     |      | μs   | Minimum time between consecutive CONVST rising edges (excluding oversampling mode) <sup>1</sup>                                                                                                      |

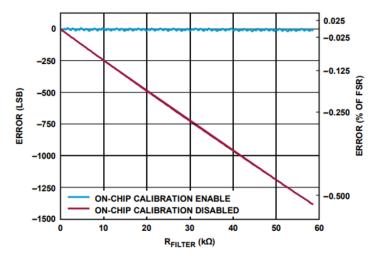

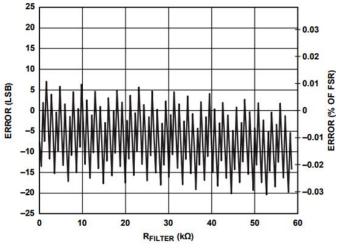

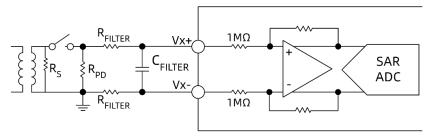

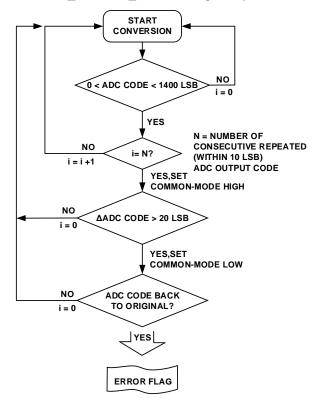

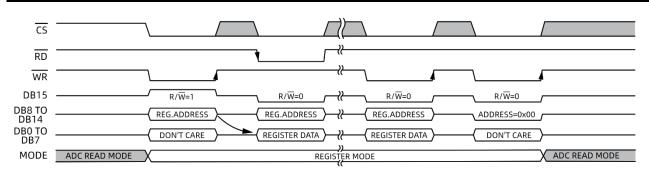

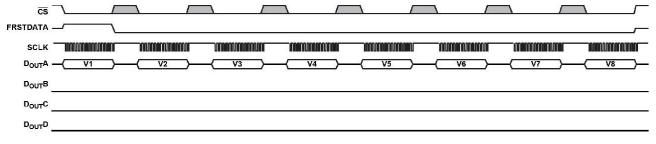

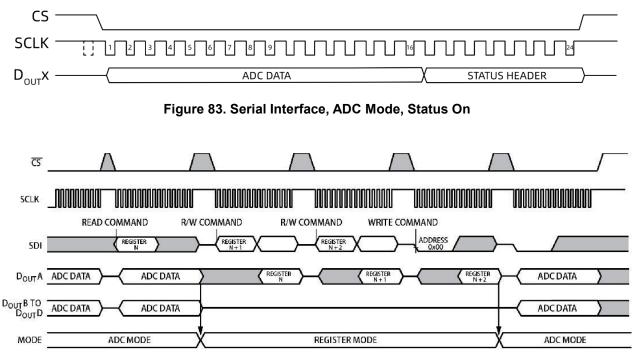

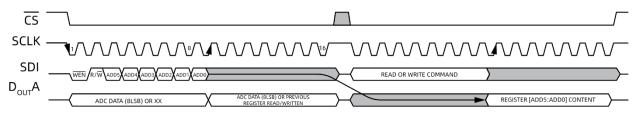

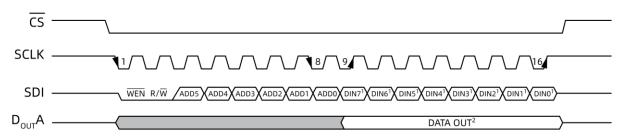

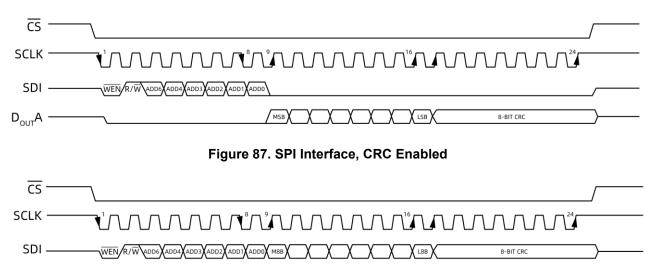

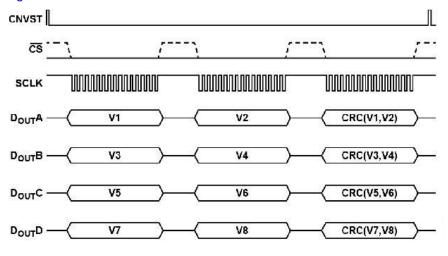

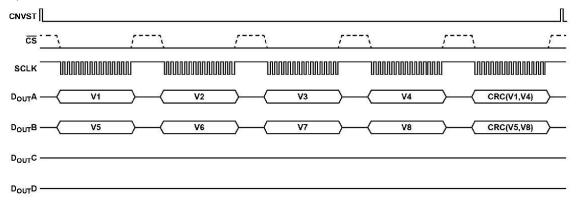

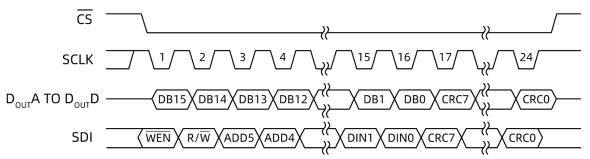

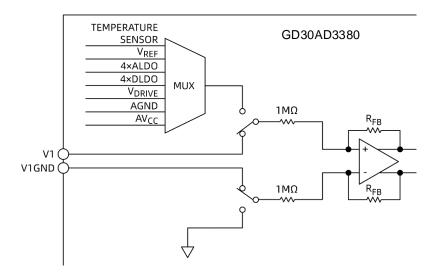

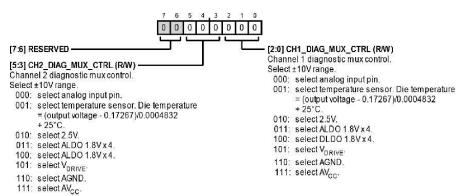

| t <sub>LP_CNV</sub> | 80   |     |      | ns   | CONVST low level pulse width                                                                                                                                                                         |