# 16-Channel DAS with 16-Bit、Bipolar Input、Dual-Channel Simultaneous Sampling ADC

#### 1 Features

- 16-channel, dual-way, synchronous sampling input

- Independently selectable channel input ranges

- True bipolar: ±10 V, ±5 V, ±2.5 V

- 5 V single analog supply, V DRIVE supply voltage: 2.3 V to 3.6 V

- · Fully integrated data acquisition solution

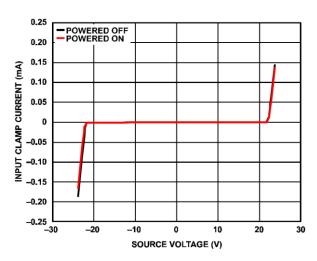

- Analog input clamp protection

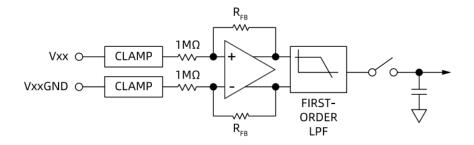

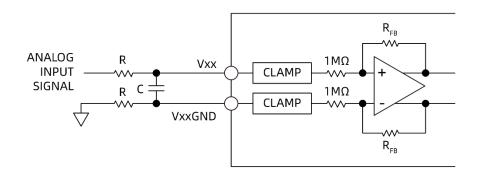

- Input buffer with 1  $M\Omega$  analog input impedance

- First order anti-aliasing analog filter

- On-chip precision voltage reference and reference voltage buffer

- Dual-channel 16-bit Successive

Approximation Register (SAR) ADC

- Throughput rate: 2×1 MSPS

- Oversampling capability provided by digital filter

- Flexible sequencer, supporting burst mode

- · Flexible parallel/serial interface

- SPI/QSPI/MICROWIRE/DSP compatible

- Hardware/Software Configuration

- performance

- Signal-to-Noise Ratio (SNR): 90.5 dB (1 MSPS)

- Total Harmonic Distortion (THD): -103 dB

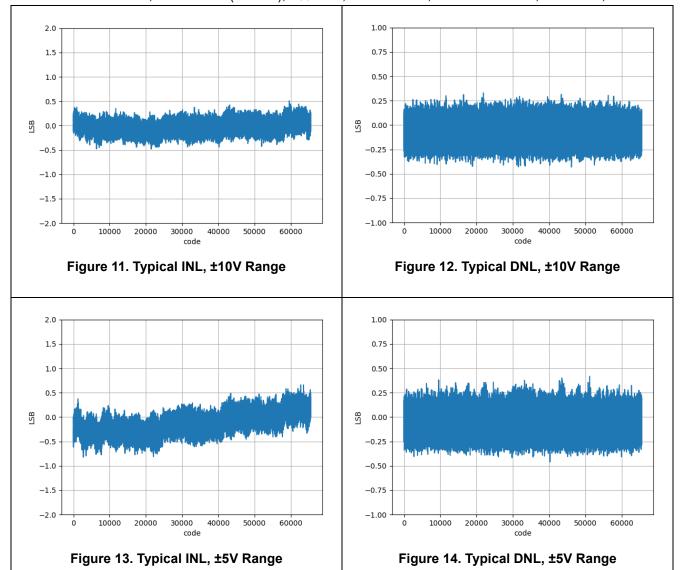

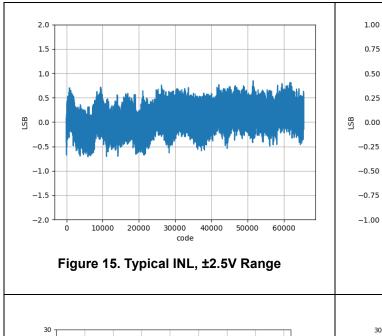

- ±1 LSB INL (typ), ±0.99 LSB DNL (max)

- 7 kV ESD rating on analog input channels

- On-chip self-test function

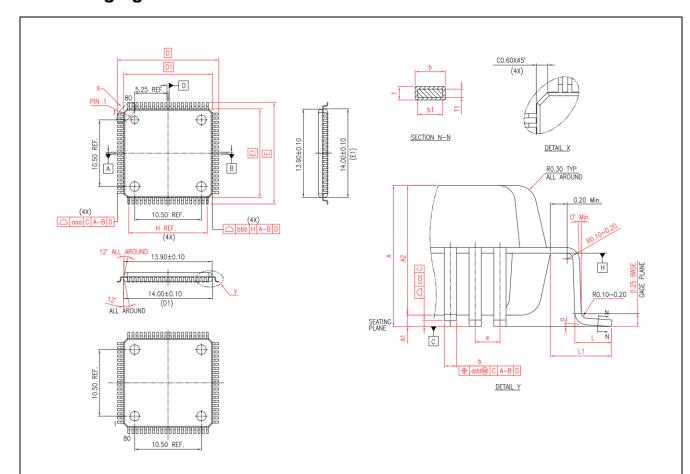

- 80-pin LQFP package

## 2 Application

- · Power line monitoring

- Protection relay

- Multiphase Motor Control

- Instrumentation and control systems

- Data Acquisition System (DAS)

## 3 Description

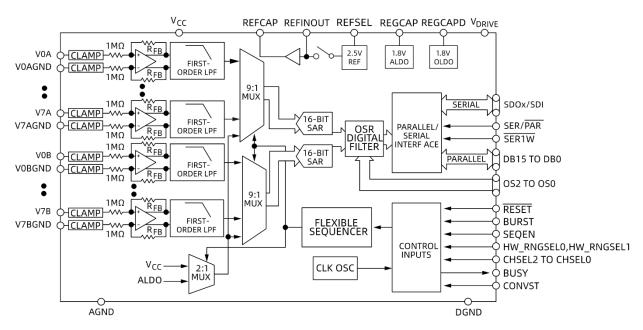

The GD30AD33G1 is a 16-bit DAS that supports dual-channel simultaneous sampling of 16 channels. The GD30AD33G1 operates from a single 5 V power supply and can handle  $\pm 10$  V,  $\pm 5$  V, and  $\pm 2.5$  V true bipolar input signals while each pair of channels can sample at up to 1MSPS throughput and 90.5 dB SNR.

The GD30AD33G1 input clamp protection circuit can withstand voltages up to  $\pm 25$  V. Regardless of the sampling frequency, the analog input impedance of the GD30AD33G1 is 1 M $\Omega$ . It operates in a single-supply mode with on-chip filtering and high input impedance, eliminating the need for a driver op amp and external bipolar power supply.

The device integrates analog input clamp protection, a dual 16-bit charge redistribution SAR analog-to-digital converter (ADC), a flexible digital filter, 2.5 V reference and reference buffer, and high speed serial and parallel interfaces.

GD30AD33G1 is compatible with Serial Peripheral Interface (SPI)/QSPI/DSP/MIC-ROWIRE.

#### Device Information<sup>1</sup>

| PART NUMBER | PACKAGE | BODY SIZE(NOM)    |  |

|-------------|---------|-------------------|--|

| GD30AD33G1  | LQFP80  | 14.00mm x 14.00mm |  |

1. For packaging details, see *Packaging Information* section.

## **Table of Contents**

| 1   | Feat     | ures                                       |    |

|-----|----------|--------------------------------------------|----|

| 2   | Appl     | lication                                   | 1  |

| 3   | Desc     | cription                                   | 1  |

| Tab | ole of ( | Contents                                   | 2  |

| 4   | Devi     | ce Overview                                | 4  |

|     | 4.1      | Pinout and Pin Assignment                  | 2  |

|     | 4.2      | Pin Description                            | 5  |

| 5   | Para     | meter Information                          | 11 |

|     | 5.1      | Absolute Maximum Ratings                   | 11 |

|     | 5.2      | Thermal Resistance                         | 11 |

|     | 5.3      | Technical Specifications                   | 12 |

|     | 5.4      | General Timing Specifications              | 16 |

|     | 5.5      | Parallel Mode Timing Specifications        | 18 |

|     | 5.6      | Serial Mode Timing Specifications          | 20 |

|     | 5.7      | Typical Performance Characteristics        | 21 |

| 6   | Fund     | ctional Description                        | 26 |

|     | 6.1      | Converter Details                          | 26 |

|     | 6.2      | Analog Input                               | 26 |

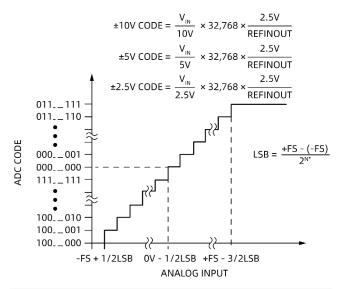

|     | 6.3      | ADC Transfer Function                      | 29 |

|     | 6.4      | Internal/External Reference Voltage Source | 30 |

|     | 6.5      | Shutdown Mode                              | 30 |

|     | 6.6      | Digital Filter                             | 30 |

| 7   | Appl     | lication Information                       | 32 |

|     | 7.1      | Functional Block Diagram                   | 32 |

|     | 7.2      | Functional Overview                        | 32 |

|     | 7.3      | Power Supply                               | 32 |

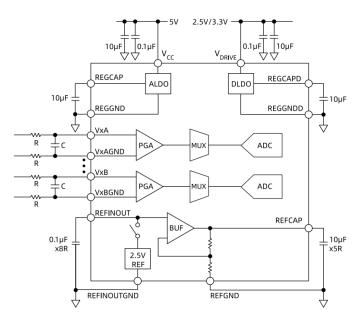

|     | 7.4      | Typical Connection                         | 32 |

| 8   | Devi     | ce Configuration                           | 34 |

|     | 8.1      | Working Mode                               | 34 |

|     | 8.2      | Internal/External Reference Voltage Source | 34 |

|     | 8.3      | Digital Interface                          | 32 |

|     | 8.4      | Hardware Mode                              | 32 |

|     | 8.5      | Software Mode                              | 35 |

|     | 8.6      | Reset Function                             | 35 |

|     | 8.7      | Pin Function Overview                      | 36 |

| 9   | Digit    | tal Interface                              | 39 |

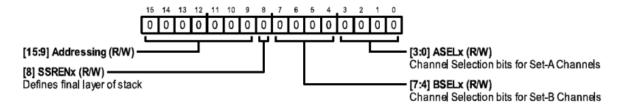

|     | 9.1      | Channel Selection                          | 39 |

|     | 9.2      | Parallel Interface                         | 40 |

|     | 9.3      | Serial Interface                           | 42 |

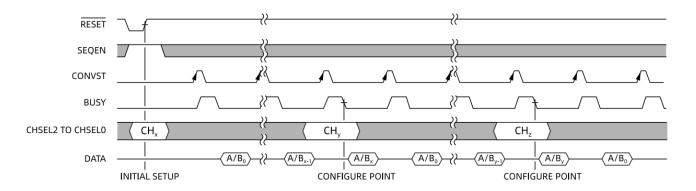

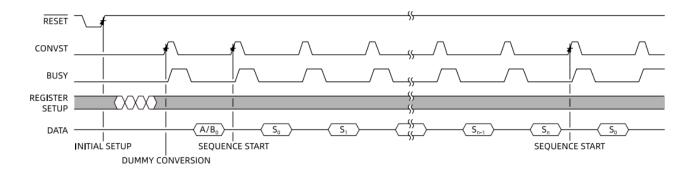

| 10  | Sequ     | uencer                                     | 46 |

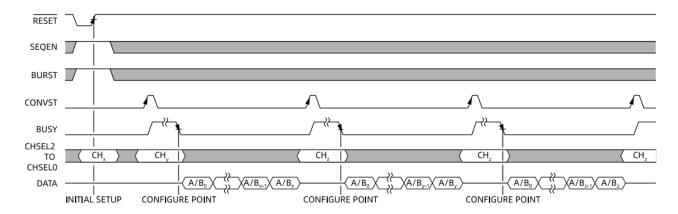

|     | 10.1     | Hardware Mode Sequencer                    | 46 |

|     |          |                                            |    |

|    | 10.2 | Software Pattern Sequencer | 47 |

|----|------|----------------------------|----|

|    | 10.3 | Burst Sequencer            | 47 |

| 11 | Diag | nosis                      |    |

|    | 11.1 | Diagnostic Channel         |    |

|    | 11.2 | Interface Self-Test        |    |

|    | 11.3 | CRC                        |    |

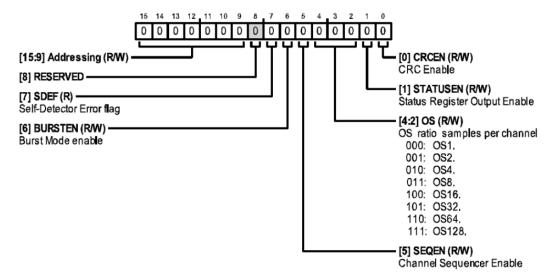

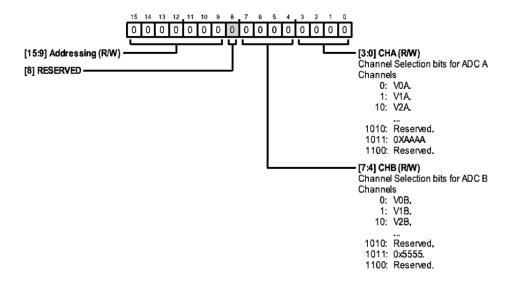

| 12 | Regi | ster Summary               |    |

|    | 12.1 | Addressing Register        |    |

|    | 12.2 | Configuration Registers    |    |

|    | 12.3 | Channel Register           |    |

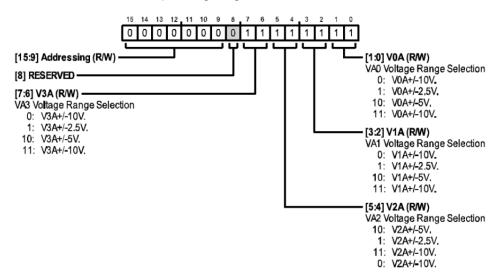

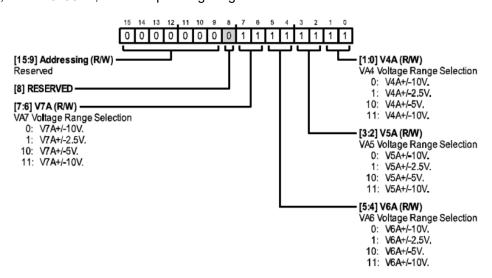

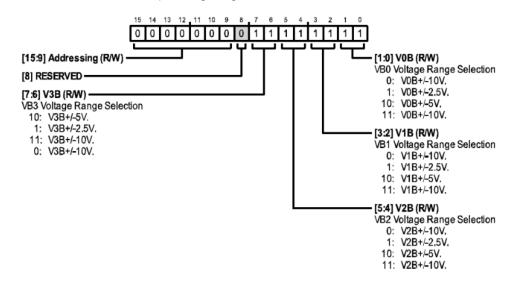

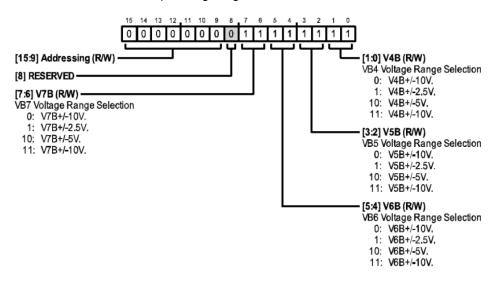

|    | 12.4 | Input Range Register       |    |

|    | 12.5 | Sequencer Stack Registers  |    |

|    | 12.6 | Status Register            |    |

| 13 | Pack | aging Information          |    |

| 14 |      | ring Information           |    |

| 15 |      | sion History               |    |

#### 4 Device Overview

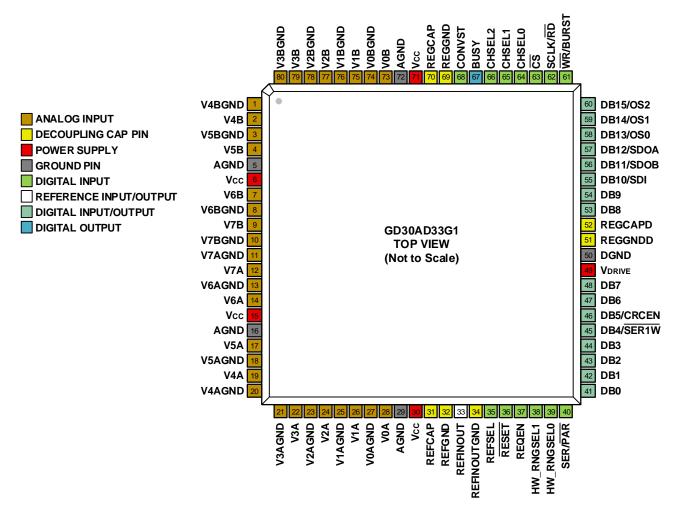

## 4.1 Pinout and Pin Assignment

Figure 1. Pin Configuration

## 4.2 Pin Description

| PINS              |               | PIN               | FUNCTION                                                                                                                                                                                                |  |  |

|-------------------|---------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME <sup>2</sup> | NUM           | TYPE <sup>1</sup> | FUNCTION                                                                                                                                                                                                |  |  |

| V4BGND            | 1             | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V4B.                                                                                                                              |  |  |

| V4B               | 2             | Al                | Channel 4 Analog Input, ADC B.                                                                                                                                                                          |  |  |

| V5BGND            | 3             | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V5B.                                                                                                                              |  |  |

| V5B               | 4             | Al                | Channel 5 Analog Input, ADC B.                                                                                                                                                                          |  |  |

| AGND              | 5, 16, 29, 72 | Р                 | Analog power ground pin.                                                                                                                                                                                |  |  |

| Vcc               | 6, 15, 30, 71 | Р                 | Analog supply voltage, 4.7 V to 5.25 V. This is the supply voltage for the internal front-end amplifier and ADC core. These pins should be decoupled to AGND with 0.1 µF and 10 µF parallel capacitors. |  |  |

| V6B               | 7             | Al                | Channel 6 Analog Input, ADC B.                                                                                                                                                                          |  |  |

| V6BGND            | 8             | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V6B.                                                                                                                              |  |  |

| V7B               | 9             | Al                | Channel 7 Analog Input, ADC B.                                                                                                                                                                          |  |  |

| V7BGND            | 10            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V7B.                                                                                                                              |  |  |

| V7AGND            | 11            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V7A.                                                                                                                              |  |  |

| V7A               | 12            | Al                | Channel 7 Analog Input, ADC A.                                                                                                                                                                          |  |  |

| V6AGND            | 13            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V6A.                                                                                                                              |  |  |

| V6A               | 14            | Al                | Channel 6 Analog Input, ADC A.                                                                                                                                                                          |  |  |

| V5A               | 17            | Al                | Analog input V5A.                                                                                                                                                                                       |  |  |

| V5AGND            | 18            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V5A.                                                                                                                              |  |  |

| V4A               | 19            | Al                | Analog input V4A.                                                                                                                                                                                       |  |  |

| V4AGND            | 20            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V4A.                                                                                                                              |  |  |

| V3AGND            | 21            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V3A.                                                                                                                              |  |  |

| V3A               | 22            | Al                | Channel 3 Analog Input, ADC A.                                                                                                                                                                          |  |  |

| V2AGND            | 23            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V2A.                                                                                                                              |  |  |

| V2A               | 24            | Al                | Channel 2 Analog Input, ADC A.                                                                                                                                                                          |  |  |

| V1AGND            | 25            | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin V1A.                                                                                                                              |  |  |

| V1A               | 26            | Al                | Channel 1 Analog Input, ADC A.                                                                                                                                                                          |  |  |

| PINS PIN          |        | PIN               | FUNCTION                                                                     |  |  |

|-------------------|--------|-------------------|------------------------------------------------------------------------------|--|--|

| NAME <sup>2</sup> | NUM    | TYPE <sup>1</sup> | FUNCTION                                                                     |  |  |

| V0AGND            | 27     | AIGND             | Analog input ground pin. This pin corresponds to the analog input pin V0A.   |  |  |

| V0A               | 28     | Al                | Channel 0 Analog Input, ADC A.                                               |  |  |

|                   |        |                   | Reference Voltage Buffer Output Force/Sense Pin. Decouple this pin           |  |  |

| REFCAP            | 31     | CAP               | to AGND with a low effective series resistance (ESR), 10 µF, X5R             |  |  |

| REFCAP            | 31     | CAP               | ceramic capacitor as close to the REFCAP pin as possible. The                |  |  |

|                   |        |                   | voltage on this pin is typically 4.096V.                                     |  |  |

| REFGND            | 32     | CAP               | Reference voltage ground pin. This pin should be connected to AGND.          |  |  |

|                   |        |                   | Reference Voltage Input/Reference Voltage Output. When the                   |  |  |

|                   |        |                   | REFSEL pin is set to logic high, this pin provides the 2.5V on-chip          |  |  |

|                   |        |                   | reference voltage for external use. Alternatively, the REFSEL pin can        |  |  |

|                   |        |                   | be set to logic low to disable the internal reference voltage and apply      |  |  |

| DEFINOUT          | 22     | DEE               | a 2.5V external reference voltage to this input. Decoupling of this pin      |  |  |

| REFINOUT          | 33     | REF               | is required whether using an internal or external reference voltage. A       |  |  |

|                   |        |                   | 100nF X8R capacitor should be connected between the REFINOUT                 |  |  |

|                   |        |                   | pin and REFINOUTGND as close to the REFINOUT pin as possible. If             |  |  |

|                   |        |                   | an external reference voltage source is used, a $10k\Omega$ series resistor  |  |  |

|                   |        |                   | should be connected to this pin to limit the reference signal bandwidth.     |  |  |

| REFINOUTGND       | 34     | CAP               | Reference voltage input and reference voltage output ground pins.            |  |  |

|                   |        |                   | Internal/External Reference Select Input. REFSEL is a logic input. If        |  |  |

|                   |        |                   | this pin is set to logic high, the internal reference mode is selected and   |  |  |

|                   |        | DI                | enabled. If this pin is set to logic low, the internal reference is disabled |  |  |

| REFSEL            | 35     |                   | and an external reference must be applied to the REFINOUT pin.               |  |  |

|                   |        |                   | When full reset is released, the signal state is latched and another full    |  |  |

|                   |        |                   | reset is required to reconfigure.                                            |  |  |

|                   |        |                   | Reset Input. Full and partial reset options are available. The type of       |  |  |

| DECET             | 26     | DI                | reset is determined by the RESET pulse length. When RESET held               |  |  |

| RESET             | 36     | DI                | low, the device is placed in shutdown mode. See Reset Function               |  |  |

|                   |        |                   | section for details.                                                         |  |  |

|                   |        |                   | Channel Sequencer Enable Input (Hardware Mode Only). When                    |  |  |

|                   |        |                   | SEQEN is tied low, the sequencer is disabled. When SEQEN is high,            |  |  |

|                   |        |                   | the sequencer is enabled (limited functionality in hardware mode).           |  |  |

| SEQEN             | 37     | DI                | See the                                                                      |  |  |

| SEQEN             | 37     | Di                |                                                                              |  |  |

|                   |        |                   | Sequencer. When full reset is released, the signal state is latched and      |  |  |

|                   |        |                   | another full reset is required to reconfigure. In software mode, this pin    |  |  |

|                   |        |                   | must be connected to DGND.                                                   |  |  |

|                   |        |                   | Hardware/Software Mode Select, Hardware Mode Range Select Input.             |  |  |

| HW_RNGSEL1        | 38, 39 | DI                | Hardware/Software Mode Select is latched on full reset. Range                |  |  |

| HW_RNGSEL0        | JU, J9 | Di                | selection in Hardware Mode is not latched.                                   |  |  |

|                   |        |                   | HW_RNGSELx = 00: Software mode; GD30AD33G1 is configured via                 |  |  |

| PINS                  |                | PIN               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME <sup>2</sup>     | NUM            | TYPE <sup>1</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                       |                |                   | software registers.  HW_RNGSELx = 01: Hardware mode; analog input range is ±2.5 V.  HW_RNGSELx = 10: Hardware mode; analog input range is ±5 V.  HW_RNGSELx = 11: Hardware mode; analog input range is ±10 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| SER/PAR               | 40             | DI                | Serial/Parallel Interface Select Input. Logic Input. If this pin is tied to a logic low, the parallel interface is selected. If this pin is tied to a logic high, the serial interface is selected. When full reset is released, the signal state is latched and another full reset is required to reconfigure                                                                                                                                                                                                                                                                                                                                                                   |  |

| DB0, DB1, DB2,<br>DB3 | 41, 42, 43, 44 | DO/DI             | Parallel output/input data bit 0 to data bit 3. In parallel mode, these pins are the output/input parallel data bits DB7 to DB0. See the   Parallel Interface section for details. In serial mode, these pins must be connected to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DB4/SER1W             | 45             | DO/DI             | Parallel Output/Input Data Bit 4/Serial Output Select. In Parallel mode, this pin acts as a three-state parallel digital output/input pin. See the <i>Parallel Interface</i> section for details.  In serial mode, this pin determines whether the serial output works on SDOA and SDOB, or only on SDOA. When SER1W is low, the serial output only works on SDOA; when SER1W is high, the serial output works on SDOA and SDOB. When the full reset is released, the signal state is latched and another full reset is required to reconfigure.                                                                                                                                 |  |

| DB5/CRCEN             | 46             | DO/DI             | Parallel Output/Input Data Bit 5/CRC Enable Input. In parallel mode, this pin acts as a three-state parallel digital input/output. While in serial mode, this pin acts as a CRC enable input. The CRCEN signal state is latched on the release of a full reset, and requires an additional full reset to reconfigure. Refer to the <i>Digital Interface</i> section for further details.  In serial mode, when CRCEN is low, there is no CRC word following the conversion results; when CRCEN is high, an extra CRC word follows the last conversion word configured by CHSELx. See the CRC section for further details.  In software mode, this pin must be connected to DGND. |  |

| DB6, DB7              | 47, 48         | DO/DI             | Parallel Output/Input Data Bit 6 and Data Bit 7. These pins act as three-state parallel digital input/outputs when SER/PAR = 0. See the <i>Parallel Interface</i> section for details.  In serial mode, when SER/PAR = 1, these pins must be connected to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| V <sub>DRIVE</sub>    | 49             | Р                 | Logic Power Input. The supply voltage at this pin determines the operating voltage of the logic interface. The nominal supply at this pin is the same as the host interface supply. This pin should be decoupled with a 0.1 $\mu$ F and 10 $\mu$ F parallel capacitor.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DGND                  | 50             | Р                 | Digital ground. This pin is the ground reference point for all digital                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PINS PIN          |            | PIN               | FUNCTION                                                                                              |  |  |

|-------------------|------------|-------------------|-------------------------------------------------------------------------------------------------------|--|--|

| NAME <sup>2</sup> | NUM        | TYPE <sup>1</sup> | FUNCTION                                                                                              |  |  |

|                   |            |                   | circuits on the GD30AD33G1 . The DGND pin must be connected to                                        |  |  |

|                   |            |                   | the DGND plane of the system.                                                                         |  |  |

| REGGNDD           | 51         | CAP               | Connect to the ground of the digital low dropout (LDO) regulator at                                   |  |  |

| NEGGNDD           | 31         | OAI               | REGCAPD (Pin 52).                                                                                     |  |  |

|                   |            |                   | Decoupling capacitor pin for the internal digital regulator voltage                                   |  |  |

| REGCAPD           | 52         | CAP               | output. This output pin should be independently decoupled to                                          |  |  |

|                   |            |                   | REGGNDD with a 10 µF capacitor. The voltage at this pin is typically                                  |  |  |

|                   |            |                   | 1.89V.                                                                                                |  |  |

|                   |            |                   | Parallel Output/Input Data Bit 9 and Data Bit 8. These pins act as                                    |  |  |

|                   |            |                   | three-state parallel digital input/outputs when SER/ $\overline{PAR}$ = 0. See the                    |  |  |

| DB8, DB9          | 53, 54     | DO/DI             | Parallel Interface section for details.                                                               |  |  |

|                   |            |                   | In serial mode, when SER/PAR = 1, these pins must be tied to                                          |  |  |

|                   |            |                   | DGND.                                                                                                 |  |  |

|                   |            |                   | Parallel Output/Input Data Bit DB10/Serial Data Output. When SER/                                     |  |  |

|                   |            |                   | PAR = 0, this pin acts as a three-state parallel digital input/output. See                            |  |  |

| DB10/SDI          | 55         | DO/DI             | the <i>Parallel Interface</i> section for details. In hardware serial mode, this                      |  |  |

|                   |            |                   | pin should be connected to DGND.  In serial mode, when SER/PAR = 1, this pin serves as the data input |  |  |

|                   |            |                   | for the SPI interface.                                                                                |  |  |

|                   |            |                   | Parallel Output/Input Data Bit 11/Serial Data Output B. When SER/                                     |  |  |

|                   |            |                   | PAR = 0, this pin acts as a three-state parallel digital input/output. See                            |  |  |

| DB11/SDOB         | 56         | DO/DI             | the <i>Parallel Interface</i> section for details.                                                    |  |  |

|                   |            |                   | In serial mode, when SER/PAR = 1, this pin functions as SDOB,                                         |  |  |

|                   |            |                   | outputting serial conversion data.                                                                    |  |  |

|                   |            |                   | Parallel Output/Input Data Bit 12/Serial Data Output A. When SER/                                     |  |  |

|                   |            |                   | PAR = 0, this pin acts as a three-state parallel digital input/output. See                            |  |  |

| DB12/SDOA         | 57         | DO/DI             | the Parallel Interface section for details.                                                           |  |  |

|                   |            |                   | In serial mode, when SER/PAR = 1, this pin functions as SDOA,                                         |  |  |

|                   |            |                   | outputting serial conversion data.                                                                    |  |  |

|                   |            |                   | Parallel Output/Input Data Bit 13, Data Bit 14, and Data Bit                                          |  |  |

|                   |            |                   | 15/Oversampling Rate Select. When SER / PAR = 0, these pins act                                       |  |  |

|                   |            |                   | as three-state parallel digital inputs/outputs. See the <i>Parallel Interface</i>                     |  |  |

| DB13/OS0,         |            |                   | section for details.                                                                                  |  |  |

| DB14/OS1,         | 58, 59, 60 | DO/DI             | In serial hardware mode, these pins control the oversampling settings.                                |  |  |

| DB15/OS2.         | DB15/OS2.  |                   | When full reset is released, the signal state is latched and requires                                 |  |  |

|                   |            |                   | another full reset to reconfigure. See the <i>Digital Filter</i> section for                          |  |  |

|                   |            |                   | details.                                                                                              |  |  |

|                   |            |                   | In software serial mode, these pins must be connected to DGND.                                        |  |  |

|                   |            |                   | Write/burst mode enable.                                                                              |  |  |

| WR/BURST          | 61         | DI                | In software parallel mode, this pin is used as a parallel interface WR.                               |  |  |

|                   |            |                   | In hardware parallel or serial mode, this pin enables BURST mode.                                     |  |  |

| PINS PIN                      |            | PIN               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------------------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME <sup>2</sup>             | NUM        | TYPE <sup>1</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                               |            |                   | When full reset is released, the signal state is latched and requires another full reset to reconfigure. See <i>Burst Sequencer</i> section for details.  In software serial mode, this pin should be connected to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| SCLK/RD                       | 62<br>63   | DI                | Serial Clock Input/Parallel Data Read Control Input. In serial mode, this pin acts as the serial clock input for data transfer. The falling edge of $\overline{CS}$ takes the data output lines SDOA and SDOB out of three-state and outputs the MSB of the conversion result. The SCLK rising edge clocks all subsequent data bits into the serial data outputs SDOA and SDOB.  In parallel mode, if both $\overline{CS}$ and RD are at logic low, the output bus is enabled.  Chip Select. This active low logic input enables data frame transmission.  In parallel mode, if both $\overline{CS}$ and RD are at logic low, the DBx output bus is enabled and the conversion results are output on the parallel |  |  |

|                               |            |                   | data bus. In serial mode, $\overline{\text{CS}}$ frames the serial read transfer and clocks out the MSB of the serial output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| CHSEL0,<br>CHSEL1,<br>CHSEL2. | 64, 65, 66 | DI                | Channel Select Input 0 to Input 2. In hardware mode, these inputs select the input channels for the next conversion in Channel Group A and Channel Group B. For example, CHSELx = 0x000 selects V0A and V0B for the next conversion; CHSELx = 0x001 selects V1A and V1B for the next conversion.  In software mode, these pins must be connected to DGND.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| BUSY                          | 67         | DO                | Busy Output. After the rising edge of CONVST, this pin goes to logic high, indicating that the conversion process has started.  The BUSY output remains high until the conversion process of the currently selected channel is complete. The falling edge of BUSY indicates that the conversion data is being latched into the output data register and will be available for reading later. The data must be read after BUSY goes low. The rising edge of CONVST has no effect when the BUSY signal is high.                                                                                                                                                                                                     |  |  |

| CONVST                        | 68         | DI                | Conversion start input for channel group A and channel group B. logic input starts conversions on the analog input channels.  For the selected analog input pair, a conversion starts when CON goes from low to high. When burst mode and oversampling mode disabled, a pair of channels is converted each time CONVST goes from low to high. In sequencer mode, when burst mode or oversampling mode is enabled, to perform the required number of conversions, CONVST only needs to go from low to high once.                                                                                                                                                                                                   |  |  |

| PII               | NS  | PIN               | FUNCTION                                                              |

|-------------------|-----|-------------------|-----------------------------------------------------------------------|

| NAME <sup>2</sup> | NUM | TYPE <sup>1</sup> | FUNCTION                                                              |

| REGGND            | 69  | CAP               | Internal analog regulator ground. This pin must be connected to the   |

|                   |     |                   | AGND plane of the system.                                             |

|                   |     |                   | Decoupling capacitor pin for the internal analog regulator voltage    |

| REGCAP            | 70  | CAP               | output. This output pin should be independently decoupled to          |

| REGUAI            | 70  | CAI               | REGGND with a 10µF capacitor. The voltage at this pin is typically    |

|                   |     |                   | 1.87V.                                                                |

| V0B               | 73  | Al                | Channel 0 Analog Input, ADC B.                                        |

| V0BGND            | 74  | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin |

| VUBGIND           | 74  | AI GND            | V0B.                                                                  |

| V1B               | 75  | Al                | Channel 1 Analog Input, ADC B.                                        |

| V1BGND            | 76  | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin |

| VIBGND            | 70  | AI GIND           | V1B.                                                                  |

| V2B               | 77  | Al                | Channel 2 Analog Input, ADC B.                                        |

| V2BGND            | 78  | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin |

| VZBGND            | 70  | KI GIVD           | V2B.                                                                  |

| V3B               | 79  | Al                | Channel 3 Analog Input, ADC B.                                        |

| V3BGND            | 80  | AI GND            | Analog input ground pin. This pin corresponds to the analog input pin |

| VODGND            | 60  | AI GND            | V3B.                                                                  |

<sup>1.</sup> Al = Analog Input, GND = Ground, P = Power, REF = Reference Voltage Input/Output, DI = Digital Input, DO = Digital Output, and CAP = Decoupling Capacitor Pin.

<sup>2.</sup> Note that throughout this data sheet, multifunction pins, such as SER/PAR, are referred to by either the entire pin name or a single function of the pin; for example, SER means only that function is relevant.

#### 5 Parameter Information

#### 5.1 Absolute Maximum Ratings

Unless otherwise stated, T<sub>A</sub> = 25 °C.

| PARAMETER                                                         | RATING                               |  |  |

|-------------------------------------------------------------------|--------------------------------------|--|--|

| Vcc to AGND                                                       | −0.3 V to +7 V                       |  |  |

| V <sub>DRIVE</sub> to AGND                                        | -0.3 V to V <sub>CC</sub> + 0.3 V    |  |  |

| Analog input voltage to AGND¹                                     | ±21 V                                |  |  |

| Digital input voltage to AGND                                     | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |  |  |

| Digital output voltage to AGND                                    | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |  |  |

| REFINOUT to AGND                                                  | -0.3 V to V <sub>CC</sub> + 0.3 V    |  |  |

| Input current to any pin other than the power supply <sup>1</sup> | ±10 mA                               |  |  |

| Operating temperature range                                       | −40 °C to +125 °C                    |  |  |

| Storage temperature range                                         | −65 °C to +150 °C                    |  |  |

| Junction temperature                                              | 150 °C                               |  |  |

| Reflow                                                            |                                      |  |  |

| Lead-tin soldering temperature (10 seconds to 30 seconds)         | 240 (+0) °C                          |  |  |

| Lead-free soldering temperature                                   | 260 (+0) °C                          |  |  |

| ESD                                                               |                                      |  |  |

| All pins except analog input                                      | 2 kV                                 |  |  |

| Analog input pins only                                            | 7 kV                                 |  |  |

<sup>1.</sup> Transient currents below 100 mA will not cause silicon controlled rectifier (SCR) latch-up.

#### 5.2 Thermal Resistance

Thermal performance is directly related to the printed circuit board (PCB) design and the operating environment, and PCB heat dissipation design must be taken seriously.  $\Theta_{JA}$  is the junction-to-ambient thermal resistance under natural convection, measured in a 1-cubic-foot sealed enclosure, and  $\Theta_{JC}$  is the junction-to-case thermal resistance.

| PACKAGE             | Θ <sub>JA</sub> | Θις | UNIT |

|---------------------|-----------------|-----|------|

| LQFP80 <sup>1</sup> | 41              | 7.5 | °C/W |

<sup>1.</sup> Thermal resistance simulation values are based on the JEDEC 2S2P thermal test board, see JEDEC JESD51.

<sup>2.</sup> Caution: Stresses equal to or exceeding the absolute maximum ratings listed above may cause permanent damage to the product. These are maximum ratings only and do not imply that the device will operate normally under these conditions or any other conditions beyond those shown in the operational section of this technical specification. Long-term operation beyond the maximum rating conditions may affect product reliability.

## 5.3 Technical Specifications

| PARAMETER                                | TEST CONDITIONS/COMMENTS                           | MIN  | TYP  | MAX   | UNIT             |

|------------------------------------------|----------------------------------------------------|------|------|-------|------------------|

| Dynamic Performance                      | f <sub>IN</sub> = 1 kHz sine wave                  |      |      |       |                  |

|                                          | No oversampling, ±10V range                        | 89   | 90.5 |       |                  |

| Signal-to-Noise Ratio (SNR) <sup>1</sup> | No oversampling, ±5V range                         | 87   | 88   |       | dB               |

|                                          | No oversampling, ±2.5V range                       | 85   | 86   |       |                  |

| O: 11 N : /D: 1 /: D /:                  | No oversampling, ±10V range                        | 88.5 | 90   |       |                  |

| Signal-to-Noise/Distortion Ratio         | No oversampling, ±5V range                         | 86   | 87.5 |       | dB               |

| (SINAD)                                  | No oversampling, ±2.5V range                       | 84   | 85.5 |       |                  |

|                                          | No oversampling, ±10V range                        |      | 92   |       |                  |

| Dynamic Range                            | No oversampling, ±5V range                         |      | 90.5 |       | dB               |

|                                          | No oversampling, ±2.5V range                       |      | 88   |       |                  |

|                                          | No oversampling, ±10V range                        |      | -102 | -93.5 |                  |

| Total Harmonic Distortion (THD)          | No oversampling, ±5V range                         |      | -103 |       | dB               |

|                                          | No oversampling, ±2.5V range                       |      | -104 |       |                  |

| Peak harmonics or spurious noise         |                                                    |      | -102 |       | dB               |

| Channel-to-channel isolation             | f <sub>IN</sub> up to 5kHz for unselected channels |      | -106 |       | dB               |

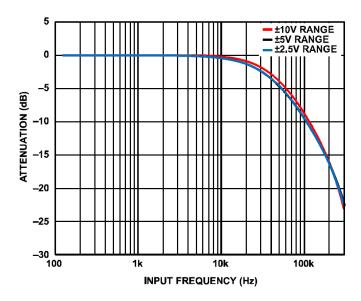

| Analog Input Filter                      |                                                    |      |      |       | •                |

| Full Davies Dandwidth                    | -3 dB                                              |      | 25   |       | 1.11=            |

| Full Power Bandwidth                     | -0.1 dB                                            |      | 3.9  |       | kHz              |

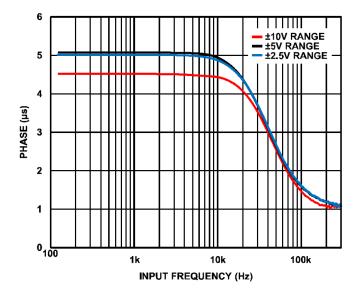

|                                          | ±10 V range                                        |      | 6.9  |       |                  |

| Phase Delay <sup>2</sup>                 | ±5V range                                          |      | 6.7  |       | μs               |

|                                          | ±2.5 V range                                       |      | 6    |       |                  |

| Phase Delay Matching                     |                                                    |      |      | 200   | ns               |

| DC Accuracy                              |                                                    |      |      |       | •                |

| Resolution                               | No missing codes                                   | 16   |      |       | Bits             |

| Differential Nonlinearity (DNL)          |                                                    |      | ±0.5 | ±0.99 | LSB <sup>4</sup> |

| Integral Nonlinearity (INL)              |                                                    |      | ±1   | ±2    | LSB              |

|                                          | ±10 V range                                        |      | ±6   |       |                  |

| Total Unadjusted Error (TUE)             | ±5V range                                          |      | ±8   |       | LSB              |

|                                          | ±2.5V range                                        |      | ±10  |       |                  |

| Positive full scale error <sup>4</sup>   |                                                    |      |      |       |                  |

|                                          | ±10V range                                         |      | ±3   | ±32   |                  |

| External reference voltage source        | ±5V range                                          |      | ±4   |       | LSB              |

|                                          | ±2.5V range                                        |      | ±5   |       | 1                |

| Internal voltage reference               | ±10V range                                         |      | ±3   |       | LSB              |

# **Technical Specifications (Continued)**

| PARAMETER                                    | TEST CONDITIONS/COMMENTS          | MIN | TYP  | MAX   | UNIT   |  |

|----------------------------------------------|-----------------------------------|-----|------|-------|--------|--|

| Positive Full Scale (PFS) Error              | External reference voltage source |     | ±2   | ±5    | nnm/°C |  |

| Drift <sup>2</sup>                           | Internal voltage reference        |     | ±3   | ±10   | ppm/°C |  |

|                                              | ±10V range                        |     | 4    |       |        |  |

| Positive Full-Scale Error Matching           | ±5V range                         |     | 4    |       | LSB    |  |

|                                              | ±2.5V range                       |     | 8    |       |        |  |

|                                              | ±10V range                        |     | ±1   | ±8    |        |  |

| Bipolar Zero Code Error                      | ±5V range                         |     | ±1   | ±10   | LSB    |  |

|                                              | ±2.5V range                       |     | ±1.5 | ±15   |        |  |

|                                              | ±10V range                        |     | ±6   | ±20.4 |        |  |

| Bipolar Zero Code Error Drift <sup>2</sup>   | ±5V range                         |     | ±3.6 |       | μV/°C  |  |

|                                              | ±2.5V range                       |     | ±2.5 |       |        |  |

|                                              | ±10V range                        |     | ±2   | ±10   |        |  |

| Bipolar Zero Code Error Matching             | ±5V range                         |     | ±3   |       | LSB    |  |

|                                              | ±2.5V range                       |     | ±3   |       |        |  |

|                                              | External reference voltage source |     |      |       |        |  |

|                                              | ±10V range                        | ±32 | LSB  |       |        |  |

| Negative Full Cools (NFC) Fores              | ±5V range ±4                      |     |      |       |        |  |

| Negative Full Scale (NFS) Error <sup>4</sup> | ±2.5V range                       |     | ±5   |       |        |  |

|                                              | Internal voltage reference        |     |      |       |        |  |

|                                              | ±10V range                        |     | ±3   |       | LSB    |  |

| Name tive full and a sum of diff?            | External reference voltage source |     | ±2   | ±5    | /°C    |  |

| Negative full scale error drift <sup>2</sup> | Internal voltage reference        |     | ±3   | 10    | ppm/°C |  |

|                                              | ±10V range                        |     | 4    |       |        |  |

| Negative Full Scale Error Matching           | ±5V range                         |     | 4    |       | LSB    |  |

|                                              | ±2.5V range                       | 8   |      |       |        |  |

| Analog Input                                 |                                   |     |      |       |        |  |

|                                              | Software/Hardware Optional        |     |      | ±10   |        |  |

| Input voltage range                          | Software/Hardware Optional        |     | ±5   | V     |        |  |

|                                              | Software/Hardware Optional        |     |      | ±2.5  |        |  |

|                                              | ±10V range                        |     | 10   |       | μA     |  |

| Analog input current                         | ±5V range                         |     | 5    |       | μA     |  |

|                                              | ±2.5V range 2.5                   |     |      |       | μA     |  |

| Input Capacitor <sup>5</sup>                 |                                   |     | 5    |       | pF     |  |

| Input Impedance                              | See Analog Input section          | 1   |      |       | МΩ     |  |

|                                              | l                                 |     |      |       | 1      |  |

# **Technical Specifications (Continued)**

| PARAMETER                                       | TEST CONDITIONS/COMMENTS              | MIN                      | TYP      | MAX   | UNIT                                  |

|-------------------------------------------------|---------------------------------------|--------------------------|----------|-------|---------------------------------------|

| Reference voltage input/out                     | put                                   | •                        |          |       | •                                     |

| Reference input voltage range                   | See the ADC Transfer Function section | 2.495                    | 2.5      | 2.505 | V                                     |

| DC leakage current                              |                                       |                          |          | ±0.1  | μA                                    |

| Input Capacitor <sup>5</sup>                    | REFSEL = 1                            |                          | 7.5      |       | pF                                    |

| Reference output voltage                        | REFINOUT                              | 2.495                    | 2.5      | 2.505 | V                                     |

| Reference source temperature                    |                                       |                          | ±3       | ±15   | nnm/°C                                |

| coefficient <sup>2</sup>                        |                                       |                          | <u> </u> | ±10   | ppm/°C                                |

| Logic Input                                     |                                       |                          |          |       |                                       |

| Input voltage                                   |                                       |                          |          |       |                                       |

| High (V <sub>INH</sub> )                        | V <sub>DRIVE</sub> = 2.7 V to 3.6 V   | 2                        |          |       | V                                     |

| Tilgit (VINH)                                   | V <sub>DRIVE</sub> = 2.3 V to 2.7 V   | 1.7                      |          |       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| 1 () /                                          | V <sub>DRIVE</sub> = 2.7 V to 3.6 V   |                          |          | 0.8   | V                                     |

| Low (V <sub>INL</sub> )                         | V <sub>DRIVE</sub> = 2.3 V to 2.7 V   |                          |          | 0.7   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Input Current (I <sub>IN</sub> )                |                                       |                          |          | ±1    | μA                                    |

| Input Capacitor (C <sub>IN</sub> ) <sup>5</sup> |                                       |                          | 5        |       | pF                                    |

| Logic Output                                    |                                       | 1                        |          |       | 1                                     |

| Output voltage                                  |                                       |                          |          |       |                                       |

| High (V <sub>OH</sub> )                         | Isource = 100 µA                      | V <sub>DRIVE</sub> - 0.2 | 2        |       | V                                     |

| Low (V <sub>OL</sub> )                          | I <sub>SINK</sub> = 100 μA            |                          |          | 0.4   | V                                     |

| Floating state leakage current                  |                                       |                          | ±0.005   | ±1    | μA                                    |

| Floating output capacitance <sup>5</sup>        |                                       |                          | 5        |       | pF                                    |

| Output Encoding                                 | Two's complement                      |                          |          |       |                                       |

| Conversion Rate                                 |                                       | -1                       |          |       |                                       |

| Conversion time                                 | Each pair of channels                 |                          | 0.55     |       | μs                                    |

| Collection time                                 | Each pair of channels                 |                          | 0.45     |       | μs                                    |

| Throughput rate                                 | Each pair of channels                 |                          |          | 1     | MSPS                                  |

| Power Requirements                              |                                       | -                        |          |       |                                       |

| Vcc                                             |                                       | 4.75                     |          | 5.25  | V                                     |

| V <sub>DRIVE</sub>                              |                                       | 2.3                      |          | 3.6   | V                                     |

| Ivec                                            |                                       |                          |          |       |                                       |

| Normal Mode                                     |                                       |                          |          |       |                                       |

| Static                                          |                                       |                          | 21       | 27    | mA                                    |

| Operational                                     | f <sub>SAMPLE</sub> = 1MSPS           |                          | 25       | 31    | mA                                    |

| Shutdown Mode                                   |                                       |                          | 4        |       | μA                                    |

## **Technical Specifications (Continued)**

| PARAMETER         | TEST CONDITIONS/COMMENTS                 | MIN | TYP | MAX  | UNIT |

|-------------------|------------------------------------------|-----|-----|------|------|

| Idrive            | Digital input = 0V or V <sub>DRIVE</sub> |     |     |      |      |

| Normal Mode       |                                          |     |     |      |      |

| Static            |                                          |     | 0.7 | 0.85 | mA   |

| Operation         | f <sub>SAMPLE</sub> = 1MSPS              |     | 4.6 | 4.9  | mA   |

| Shutdown Mode     |                                          |     | 85  |      | μA   |

| Power consumption |                                          |     |     |      |      |

| Normal Mode       |                                          |     |     |      |      |

| Static            |                                          |     | 130 | 150  | mW   |

| Operation         | f <sub>SAMPLE</sub> = 1MSPS              |     | 160 | 180  | mW   |

| Shutdown Mode     |                                          |     | 2.8 |      | mW   |

- 1. By enabling oversampling, the user can achieve 93 dB SNR, these values are valid for manual mode, in burst mode these values are reduced by approximately 1 dB.

- 2. Not production tested. Samples are tested during initial release to ensure compliance with standards.

- 3. LSB stands for least significant bit. For  $\pm 2.5$  V input range, 1LSB = 76.293  $\mu$ V; for  $\pm 5$  V input range, 1LSB = 152.58  $\mu$ V; for  $\pm 10$  V input range, 1LSB = 305.175  $\mu$ V.

- 4. The positive and negative full-scale errors of the internal reference do not include the reference error.

- 5. Simulation data support.

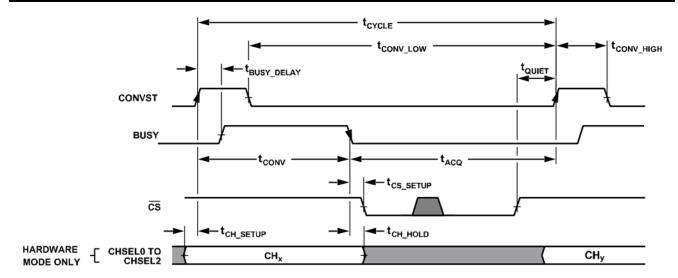

## **General Timing Specifications**

$V_{CC}$  = 4.75 V to 5.25 V,  $V_{DRIVE}$  = 2.3 V to 3.6 V,  $V_{REF}$  = 2.5 V external/internal reference,  $T_A$  = -40 °C to +125 °C, unless otherwise noted. Interface timing is tested with 30pF load capacitance and is dependent on VDRIVE and the load capacitance of the serial interface.

| PARAMETER <sup>1</sup>   | CONDITIONS                                                                      | MIN  | TYP | MAX | UNIT |

|--------------------------|---------------------------------------------------------------------------------|------|-----|-----|------|

| 1                        | Minimum time between consecutive CONVST rising edges                            | 4    |     |     |      |

| tcycle                   | (excluding burst and oversampling modes)                                        | 1    |     |     | μs   |

| tconv_low                | CONVST low level pulse width                                                    | 80   |     |     | ns   |

| t <sub>CONV_HIGH</sub>   | CONVST high level pulse width                                                   | 80   |     |     | ns   |

| tbusy_delay              | CONVST high to BUSY high (manual mode)                                          |      |     | 32  | ns   |

| tcs_setup                | BUSY falling edge to $\overline{\text{CS}}$ falling edge setup time             | 20   |     |     | ns   |

| tch_setup                | Channel selection setup time for CHSELx in hardware mode                        | 50   |     |     | ns   |

| tcн_ногр                 | Channel selection hold time of CHSELx in hardware mode                          | 20   |     |     | ns   |

| tconv                    | Conversion time for selected channel pair                                       |      | 475 | 520 | ns   |

| tacq                     | Acquisition time for the selected channel pair                                  | 480  |     |     | ns   |

| tquiet                   | CS rising edge to the next CONVST rising edge                                   | 50   |     |     | ns   |

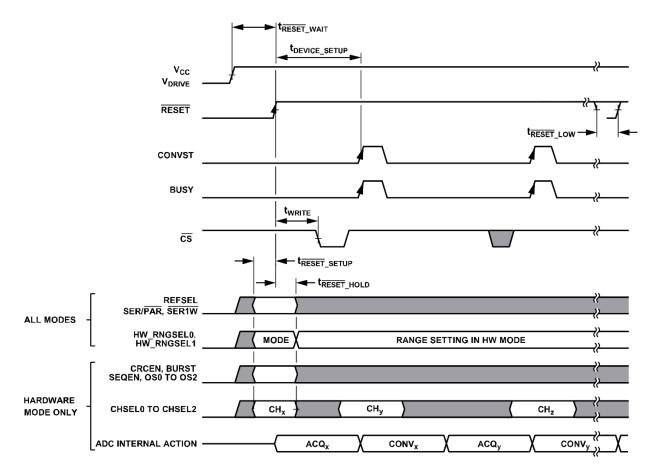

| t RESET_LOW              |                                                                                 |      |     |     |      |

| Partial Reset            | Partial RESET low level pulse width                                             | 40   |     | 500 | ns   |

| Complete reset           | Full RESET low level pulse width                                                | 1.2  |     |     | μs   |

| tdevice_setup            |                                                                                 |      |     |     |      |

| Dartiel Deset            | The time between the high level of the part CONVST and the                      | 50   |     |     | ne   |

| Partial Reset            | rising edge of RESET                                                            | 50   |     |     | ns   |

| Complete reset           | The time between the full high level of CONVST and the rising                   | 15   |     |     | ms   |

|                          | edge of RESET                                                                   |      |     |     |      |

| twrite                   |                                                                                 |      |     |     |      |

| Partial Reset            | For write operations, RESET the time between the high level and CS              | 50   |     |     | ns   |

| Complete reset           | For write operations, RESET the time between fully high and CS                  | 240  |     |     | μs   |

| t <sub>RESET</sub> _WAIT | Time between stabilizing VCC/VDRIVE and releasing RESET                         | 1    |     |     | ms   |

| treset_setup             | RESET The time that the queried hardware input must remain                      |      |     |     |      |

| - TREGET _GET GT         | stable before being released                                                    |      |     |     |      |

| Partial Reset            |                                                                                 | 10   |     |     | ns   |

| Complete reset           |                                                                                 | 0.05 |     |     | ms   |

| t RESET_HOLD             | RESET The time after release that the queried hardware input must remain stable |      |     |     |      |

| Partial Reset            |                                                                                 | 10   |     |     | ns   |

| Complete reset           |                                                                                 | 0.24 |     |     | ms   |

|                          |                                                                                 |      |     |     |      |

<sup>1.</sup> Not production tested. Samples are tested during initial release to ensure compliance with standards.

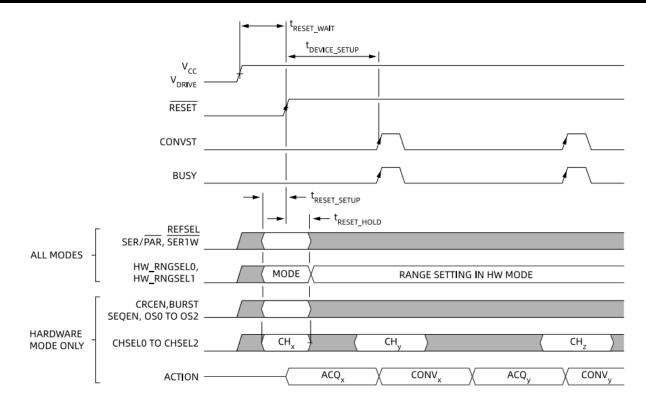

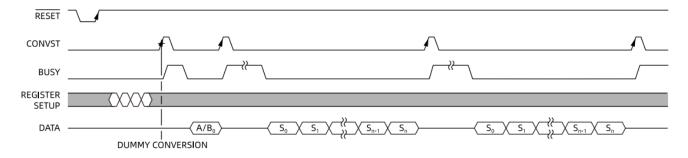

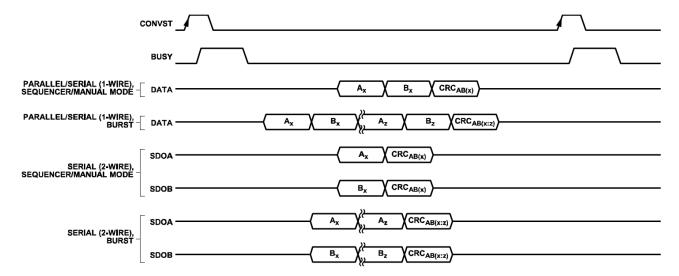

Figure 2. Universal Timing Diagram Across All Interfaces

Figure 3. Reset Timing Diagram

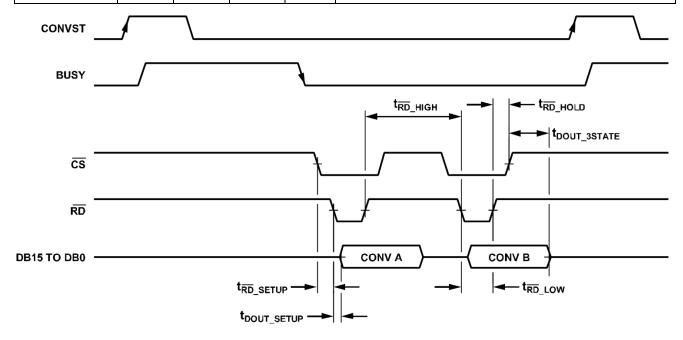

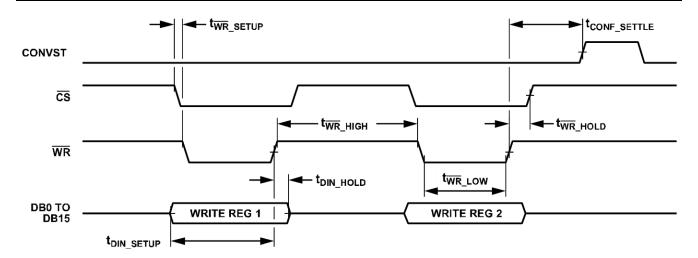

## 5.5 Parallel Mode Timing Specifications

| PARAMETER               | MIN | TYP | MAZ | UNIT | DESCRIPTION                                              |

|-------------------------|-----|-----|-----|------|----------------------------------------------------------|

| t <sub>RD_SETUP</sub>   | 0   |     |     | ns   | CS falling edge to RD falling edge setup time            |

| t <sub>RD_HOLD</sub>    | 0   |     |     | ns   | RD rising edge to CS rising edge hold time               |

| t <sub>RD_HIGH</sub>    | 10  |     |     | ns   | RD high level pulse time                                 |

| t <sub>RD_LOW</sub>     | 30  |     |     | ns   | RD low level pulse time                                  |

| t <sub>DOUT_SETUP</sub> |     |     | 30  | ns   | Data access time after the falling edge RD               |

| tdout_3STATE            |     |     | 11  | ns   | CS rising edge to DBx high impedance state               |

| twr_setup               | 10  |     |     | ns   | CS to WR set-up time                                     |

| twr_HIGH                | 20  |     |     | ns   | WR high level pulse time                                 |

| t <sub>WR_LOW</sub>     | 30  |     |     | ns   | WR low level pulse time                                  |

| twr_hold                | 10  |     |     | ns   | WR hold time                                             |

| t <sub>DIN_</sub> SETUP | 30  |     |     | ns   | Configuration data to WR set-up time                     |

| t <sub>DIN_HOLD</sub>   | 10  |     |     | ns   | Configuration data to WR hold time                       |

| <b>.</b>                | 20  |     |     | no   | Configuration data stabilization time, WR rising edge to |

| tconf_settle            | 20  |     |     | ns   | CONVST rising edge                                       |

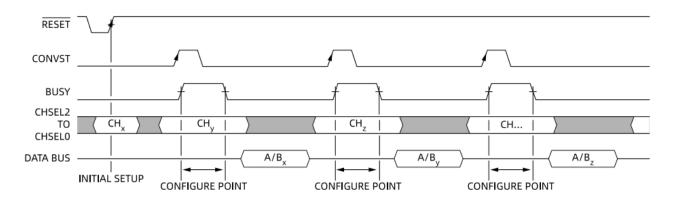

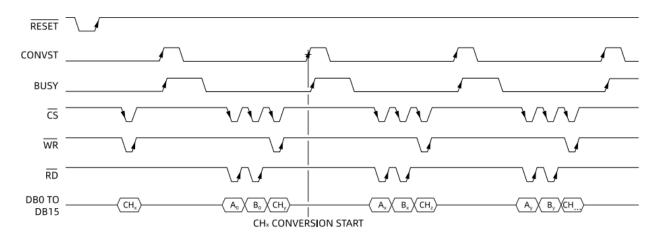

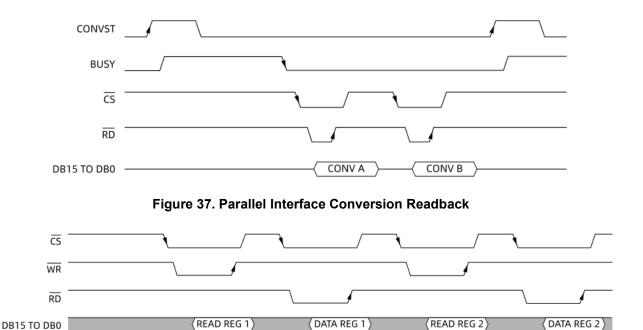

Figure 4. Parallel Read Timing Diagram

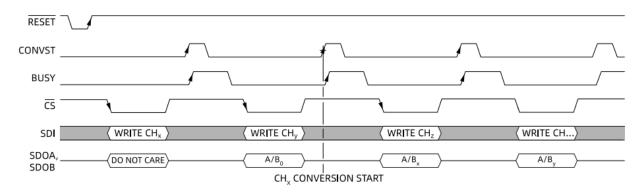

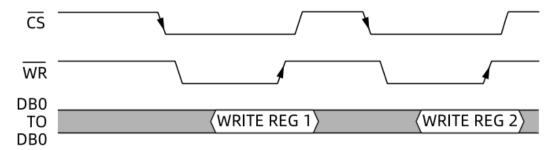

Figure 5. Parallel Write Timing Diagram

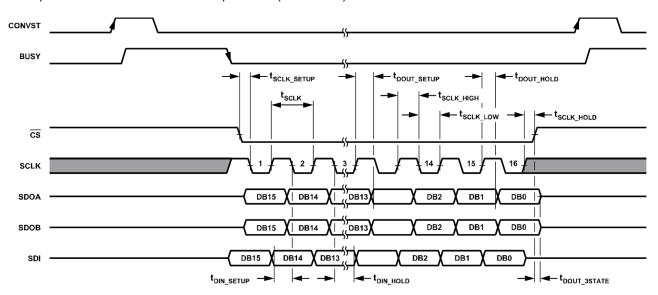

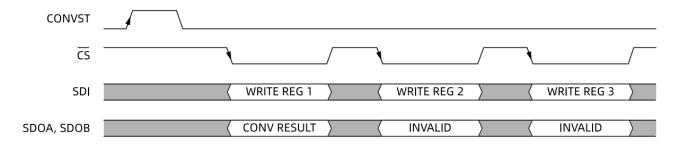

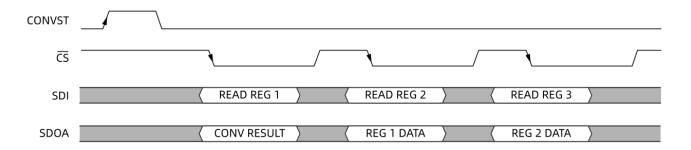

## 5.6 Serial Mode Timing Specifications

| PARAMETER                      | MIN                 | TYP | MAZ   | UNIT | DESCRIPTION                                                                              |  |

|--------------------------------|---------------------|-----|-------|------|------------------------------------------------------------------------------------------|--|

| f <sub>SCLK</sub> <sup>1</sup> |                     |     | 40/50 | MHz  | SCLK Frequency                                                                           |  |

| t <sub>SCLK</sub>              | 1/f <sub>SCLK</sub> |     |       |      | Minimum SCLK period                                                                      |  |

| tsclk_setup1                   | 10.5                |     |       | ns   | CS to SCLK falling edge set-up time, V <sub>DRIVE</sub> higher than 3V                   |  |

|                                | 13.5                |     |       | ns   | CS to SCLK falling edge set-up time, V <sub>DRIVE</sub> higher than 2.3V                 |  |

| tsclk_Hold                     | 10                  |     |       | ns   | SCLK to CS rising edge hold time                                                         |  |

| t <sub>SCLK_LOW</sub>          | 8                   |     |       | ns   | SCLK low-level pulse width                                                               |  |

| t <sub>SCLK_HIGH</sub>         | 9                   |     |       | ns   | SCLK high-level pulse width                                                              |  |

| tDOUT_SETUP <sup>1</sup>       |                     |     | 9     | ns   | SCLK data output access time after the rising edge, V <sub>DRIVE</sub> higher than 3 V   |  |

|                                |                     |     | 11    | ns   | SCLK data output access time after the rising edge, V <sub>DRIVE</sub> higher than 2.3 V |  |

| t <sub>DOUT_HOLD</sub>         | 4                   |     |       | ns   | SCLK data output access time after the rising edge                                       |  |

| t <sub>DIN_</sub> SETUP        | 10                  |     |       | ns   | SCLK data input setup time before the falling edge                                       |  |

| t <sub>DIN_HOLD</sub>          | 8                   |     |       | ns   | SCLK data input hold time after the falling edge                                         |  |

| tdout_3STATE                   |                     |     | 10    | ns   | CS rising edge to SDOx high impedance                                                    |  |

1. Depends on VDRIVE and the load capacitance (see Table 6).

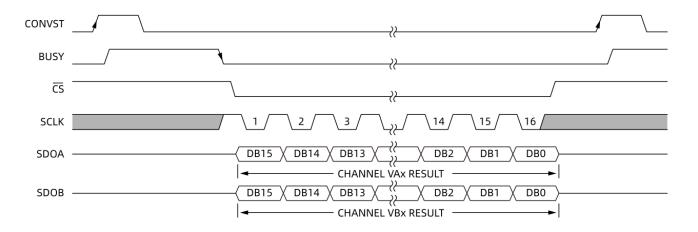

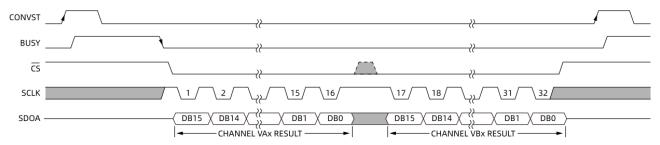

Figure 6. Serial Timing Diagram

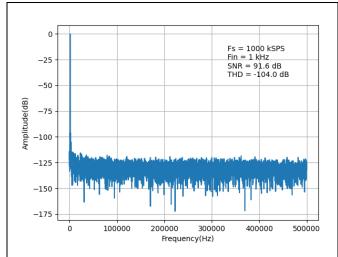

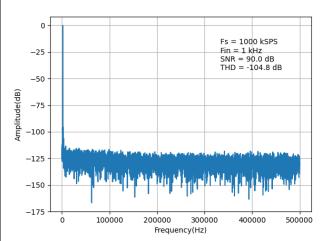

## 5.7 Typical Performance Characteristics

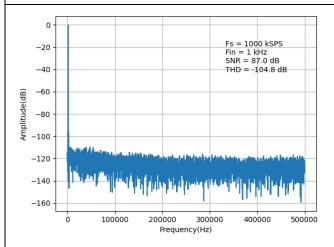

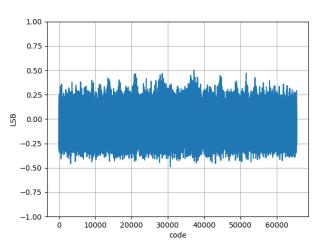

Figure 7. Fast Fourier Transform (FFT), ±10V Range

Figure 8. Fast Fourier Transform (FFT), ±5V Range

Figure 9. Fast Fourier Transform (FFT), ±2.5V Range

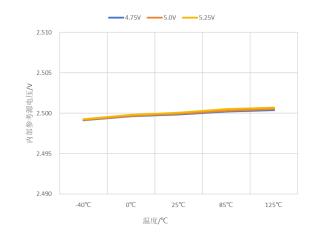

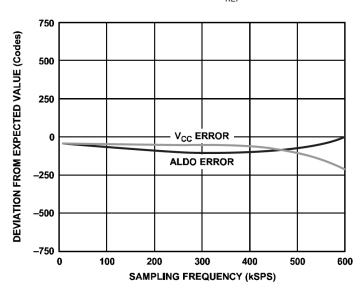

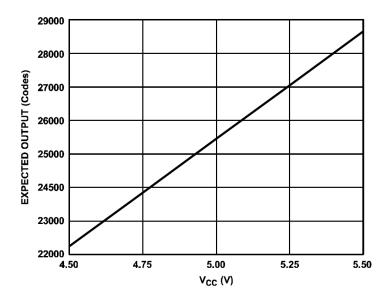

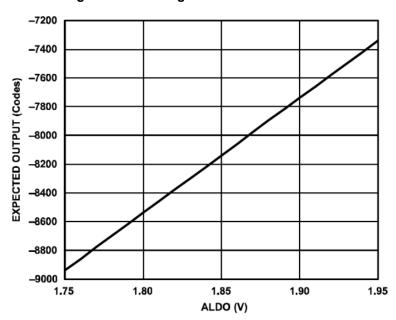

Figure 10. Internal Reference Source Temperature

Characteristics

Figure 16. Typical DNL, ±2.5V Range

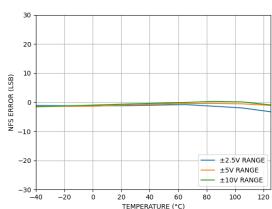

Figure 17. PFS Error vs Temperature

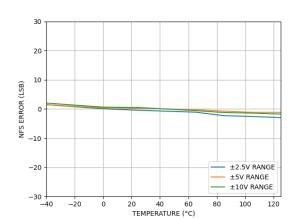

Figure 18. NFS Error vs Temperature

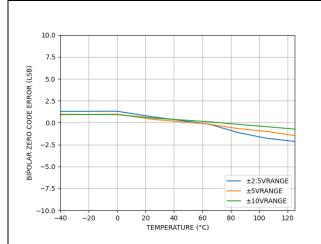

Figure 19. Bipolar Zero Code Error vs Temperature

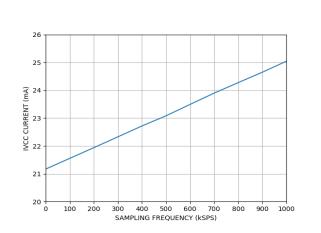

Figure 20. IVCC vs Sampling Rate

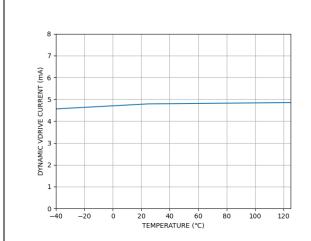

Figure 21. Dynamic VDRIVE vsTemperature

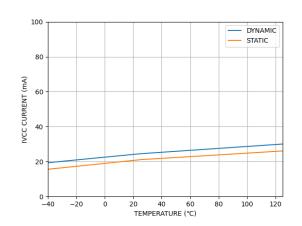

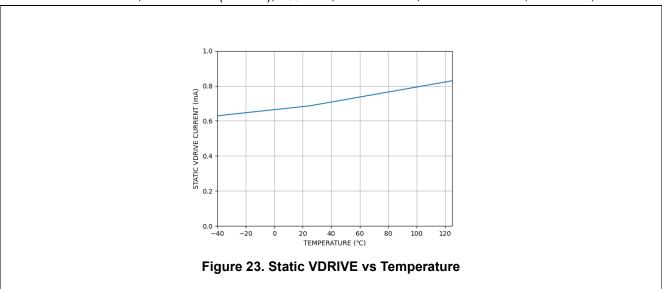

Figure 22. IVCC vs Temperature

## 6 Functional Description

#### 6.1 Converter Details

The GD30AD33G1 is a data acquisition system that uses a high-speed, low-power, charge redistribution successive approximation analog-to-digital converter (ADC) that can perform dual-channel simultaneous sampling of 16 analog input channels. The analog inputs of the GD30AD33G1 can accept true bipolar input signals. The analog input range options are ±10 V, ±5 V, and ±2.5 V. The GD30AD33G1 is powered by a single 5 V power supply.

The GD30AD33G1 has built-in input clamp protection, input signal scaling amplifier, first-order anti-aliasing filter, on-chip reference voltage source, reference voltage buffer, dual high-speed ADC, digital filter, flexible sequencer, and high-speed parallel and serial interfaces.

By controlling the HW\_RNGSELx pins, the GD30AD33G1 can work in hardware or software mode. In hardware mode, the GD30AD33G1 is configured by pin control. In software mode, the GD30AD33G1 is configured by control registers (accessed through serial or parallel interfaces).

#### 6.2 Analog Input

#### 6.2.1 Analog Input Channel Selection