# General-Purpose, Micro-Power 1MHz, RRIO, Precision Amplifiers

# 1 Features

- Precision: 1.0 mV Maximum Positive Input Offset Voltage

- Low Noise: 29 nV/√Hz at 1 kHz

- 1 MHz GBW for Unity-Gain Stable

- Micro-Power: 85 µA Supply Current Per Amplifier

- Single 1.8V to 5.5V Supply Voltage Range at 0°C to 70°C

- Rail-to-Rail Input and Output

- Internal RF/EMI Filter

- Extended Temperature Range: -40°C to +125°C

# 2 Applications

- Battery-Powered Instruments:

Consumer, Industrial, Medical, Notebooks

- Wireless Chargers

- Audio Outputs

- Sensor Signal Conditioning:

Sensor Interfaces, Loop-Powered, Active Filters

- Wireless Sensors:

- Home Security, Remote Sensing, Wireless Metering

# 3 Description

The GD30AP321A and GD30AP358A family of singleand dual-channel amplifiers provides input offset voltage correction for positive low offset (maximum 1.0mV) and drift  $(1\mu V/^{\circ}C)$  through the use of proprietary techniques. Featuring rail-to-rail input and output swings, and low quiescent current (typical 85 µA) combined with a wide bandwidth of 1MHz and very low noise  $(29nV/\sqrt{Hz} \text{ at 1kHz})$  makes this family very attractive for a variety of battery-powered applications such as handsets, tablets, notebooks, and portable medical devices. The low input bias current supports these amplifiers to be used in applications with mega-ohm source impedances.

The robust design of the GD30AP321A and GD30AP358A amplifiers provides ease-of-use to the circuit designer: unity-gain stability with capacitive loads of up to 500pF, integrated RF/EMI rejection filter, no phase reversal in overdrive conditions, and high electrostatic discharge (ESD) protection (5kV HBM). The GD30AP321A and GD30AP358A amplifiers are optimized for operation at voltages as low as +1.8V ( $\pm$ 0.9V) and up to +5.5V ( $\pm$ 2.75V) at the temperature range of 0°C to 70°C, and operation at voltages from +2.0V ( $\pm$ 1.0V) to +5.5V ( $\pm$ 2.75V) over the extended temperature range of -40°C to +125°C.

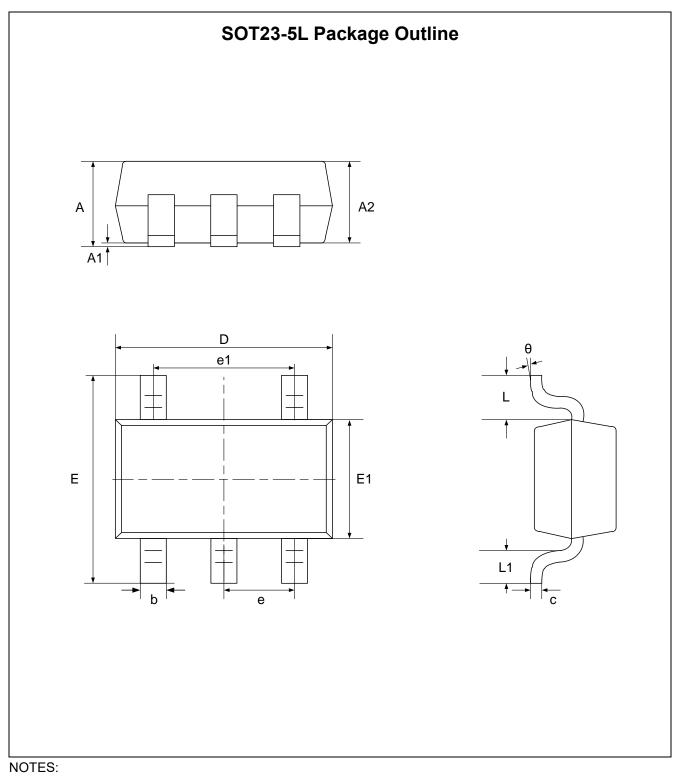

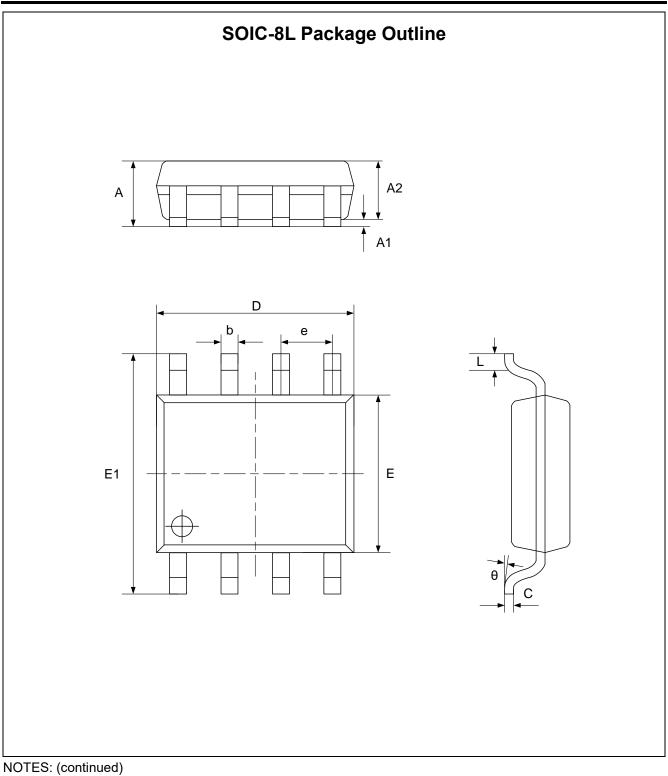

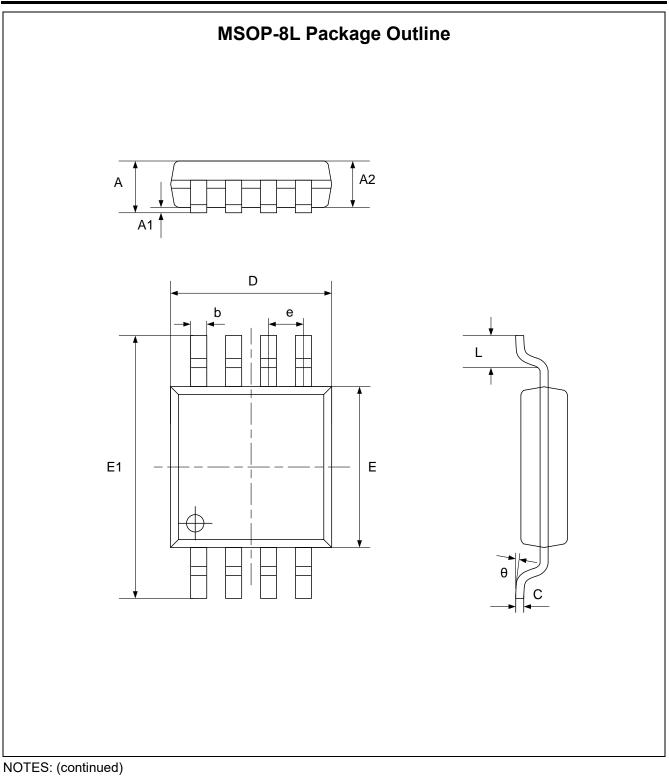

The GD30AP321A (single) is available in SOT23-5L package. The GD30AP358A (dual) is offered in SOIC-8L and MSOP-8L packages.

| Device information |          |                 |  |  |  |

|--------------------|----------|-----------------|--|--|--|

| PART NUMBER        | PACKAGE  | BODY SIZE (NOM) |  |  |  |

| GD30AP321A         | SOT23-5L | 2.92mm x 1.60mm |  |  |  |

| GD30AP358A         | SOIC-8L  | 4.90mm x 3.92mm |  |  |  |

| GD30AP358A         | MSOP-8L  | 3.00mm x 3.00mm |  |  |  |

#### **Device Information<sup>1</sup>**

1. For all available packages, see the *Package Information* and *Ordering Information* at the end of data sheet.

# **Table of Contents**

| 1   | Feat               | Features1                                    |    |  |  |  |  |

|-----|--------------------|----------------------------------------------|----|--|--|--|--|

| 2   | Арр                | lications                                    | 1  |  |  |  |  |

| 3   | Des                | cription                                     | 1  |  |  |  |  |

| Tab | ole of             | Contents                                     | 2  |  |  |  |  |

| 4   | Devi               | ce Overview                                  | 3  |  |  |  |  |

|     | 4.1                | Pinout and Pin Assignment                    | 3  |  |  |  |  |

|     | 4.2                | Pin Description                              | 3  |  |  |  |  |

| 5   | Para               | meter Information                            | 4  |  |  |  |  |

|     | 5.1                | Absolute Maximum Ratings                     | 4  |  |  |  |  |

|     | 5.2                | Recommended Operation Conditions             | 4  |  |  |  |  |

|     | 5.3                | Electrical Sensitivity                       | 4  |  |  |  |  |

|     | 5.4                | Thermal Characteristics                      | 4  |  |  |  |  |

|     | 5.5                | Electrical Characteristics                   | 5  |  |  |  |  |

|     | 5.6                | Typical Characteristics                      | 7  |  |  |  |  |

| 6   | Fun                | ctional Description                          | 10 |  |  |  |  |

|     | 6.1                | Operating Voltage                            | 10 |  |  |  |  |

|     | 6.2                | Rail-to-Rail Input                           | 10 |  |  |  |  |

|     | 6.3                | Input EMI Filter and Clamp Circuit           | 11 |  |  |  |  |

|     | 6.4                | Rail-to-Rail Output                          | 11 |  |  |  |  |

|     | 6.5                | Capacitive Load and Stability                | 11 |  |  |  |  |

|     | 6.6                | Overload Recovery                            | 12 |  |  |  |  |

|     | 6.7                | EMI Rejection Ratio                          | 13 |  |  |  |  |

|     | 6.8                | Input-to-Output Coupling                     | 13 |  |  |  |  |

|     | 6.9                | Maximizing Performance Through Proper Layout | 13 |  |  |  |  |

| 7   | Арр                | lication Information                         | 15 |  |  |  |  |

|     | 7.1                | Typical Application Circuit                  | 15 |  |  |  |  |

| 8   | Pacl               | cage Information                             | 18 |  |  |  |  |

|     | 8.1                | Outline Dimensions                           | 18 |  |  |  |  |

|     | 8.2                | Recommended Land Pattern                     | 24 |  |  |  |  |

| 9   | Orde               | ering Information                            | 27 |  |  |  |  |

| 10  | 0 Revision History |                                              |    |  |  |  |  |

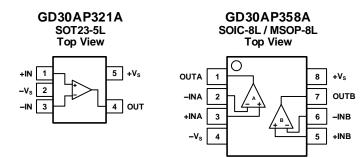

## 4 Device Overview

## 4.1 Pinout and Pin Assignment

## 4.2 Pin Description

| NAME | PIN TYPE <sup>1</sup> | FUNCTION                                                                                                                                                                              |

|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IN  | I                     | Inverting input of the amplifier. The voltage range is from (Vs <sub>-</sub> – 0.1V) to (Vs <sub>+</sub> + 0.1V).                                                                     |

| +IN  | I                     | Non-inverting input of the amplifier. This pin has the same voltage range as –IN.                                                                                                     |

| +Vs  | Р                     | Positive power supply. The voltage is from 2.0V to 5.5V. Split supplies are possible as long as the voltage between $V_{S+}$ and $V_{S-}$ is from 2.0V to 5.5V.                       |

| -Vs  | Р                     | Negative power supply. It is normally tied to ground. It can also be tied to a voltage other than ground as long as the voltage between $V_{S^+}$ and $V_{S^-}$ is from 2.0V to 5.5V. |

| OUT  | 0                     | Amplifier output.                                                                                                                                                                     |

1. I = Input, O = Output, P = Power.

# 5 Parameter Information

## 5.1 Absolute Maximum Ratings

In accordance with the Absolute Maximum Rating System (IEC 60134). Exceeding the operating temperature range (unless otherwise noted)<sup>1</sup>

| SYMBOL                 | PARAMETER                                   | MIN                  | MAX                   | UNIT |

|------------------------|---------------------------------------------|----------------------|-----------------------|------|

| $V_{S^+}$ to $V_{S^-}$ | Supply Voltage                              |                      | 10.0                  | V    |

| VI                     | Signal Input Voltage                        | V <sub>S-</sub> -0.5 | V <sub>S+</sub> + 0.5 | V    |

| h                      | Signal Input Current                        | -10                  | 10                    | mA   |

|                        | Output Short-Circuit                        |                      | Continuous            | s    |

| TJ                     | Junction Temperature, T <sub>J</sub>        |                      | 150                   | °C   |

| T <sub>stg</sub>       | Storage Temperature Range, T <sub>stg</sub> | -65                  | +150                  | °C   |

|                        | Lead Temperature Range (Soldering 10 sec)   |                      | 260                   | °C   |

The maximum ratings are the limits to which the device can be subjected without permanently damaging the device. Note that the device is not guaranteed to operate properly at the maximum ratings. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

### 5.2 Recommended Operation Conditions

| SYMBOL <sup>1</sup>                 | PARAMETER                                                   |        | TYP MAX               | UNIT |

|-------------------------------------|-------------------------------------------------------------|--------|-----------------------|------|

| Via to Via                          | Input supply voltage range( $T_A = 0^{\circ}C$ to +70°C)    | 1.8    | 5.5                   | V    |

| V <sub>S</sub> – to V <sub>S+</sub> | Input supply voltage range( $T_A = -40^{\circ}C$ to +125°C) | 2.0    | 5.5                   | V    |

| Vсм                                 | Common-mode voltage range                                   | Vs 0.1 | V <sub>S+</sub> + 0.1 | V    |

| T <sub>A</sub>                      | Operating temperature range                                 | -40    | +125                  | °C   |

1. The device is not guaranteed to function outside of its operating conditions.

### 5.3 Electrical Sensitivity

| SYMBOL                | CONDITIONS                                                            | VALUE | UNIT |

|-----------------------|-----------------------------------------------------------------------|-------|------|

| V <sub>ESD(HBM)</sub> | Human-body model (HBM), per MIL-STD-883J / Method 3015.9 <sup>1</sup> | ±5000 | V    |

| V <sub>ESD(CDM)</sub> | Charge-device model (CDM), per ESDA/JEDEC JS-002-2014 <sup>2</sup>    | ±2000 | V    |

| Vesd(MM)              | Machine model (MM), per JESD22-A115C                                  | ±250  | V    |

1. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

2. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 5.4 Thermal Characteristics

| SYMBOL <sup>1</sup> | CONDITIONS                   | PACKAGE  | VALUE | UNIT |

|---------------------|------------------------------|----------|-------|------|

|                     |                              | SOT23-5L | 190   |      |

| Θ <sub>JA</sub>     | A Package Thermal Resistance | MSOP-8L  | 216   | °C/W |

|                     |                              | SOIC-8L  | 125   |      |

1. Thermal characteristics are based on simulation, and meet JEDEC document JESD51-7.

## 5.5 Electrical Characteristics

$V_s = 5.0 \text{ V}, V_{CM} = V_s /2, V_0 = V_s /2$ , and  $R_L = 10k\Omega$  connected to  $V_s /2, T_A = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply over the specified temperature range,  $T_A = -40$  to  $+125^{\circ}C$ .

| SYMBOL          | PARAMETER                         | CONDITIONS                                                    | MIN                   | ТҮР  | MAX                   | UNIT              |

|-----------------|-----------------------------------|---------------------------------------------------------------|-----------------------|------|-----------------------|-------------------|

| OFFSET          | VOLTAGE                           |                                                               |                       |      |                       |                   |

| Vos             | Input offset voltage              |                                                               | 0                     | +0.5 | +1                    | mV                |

| dVos/d⊤         | Offset voltage drift <sup>1</sup> | T <sub>A</sub> = -40 to +125°C                                |                       | ±1   | 3                     | μV/°C             |

|                 |                                   | $V_{\rm S}$ = 2.0 to 5.5 V, $V_{\rm CM}$ < $V_{\rm S^+}$ – 2V | 80                    | 106  |                       |                   |

| PSRR            | Power supply rejection ratio      | T <sub>A</sub> = -40 to +125°C                                | 75                    |      |                       | dB                |

| INPUT BI        | AS CURRENT                        |                                                               |                       |      |                       |                   |

|                 |                                   |                                                               |                       | 1    |                       |                   |

| IB              | Input bias current <sup>1</sup>   | T <sub>A</sub> = +85°C                                        |                       | 150  |                       | pА                |

|                 |                                   | T <sub>A</sub> = +125°C                                       |                       | 500  |                       |                   |

| los             | Input offset current <sup>1</sup> |                                                               |                       | 5    |                       | pА                |

| NOISE           |                                   |                                                               |                       |      |                       |                   |

| Vn              | Input voltage noise               | f = 0.1 to 10 Hz                                              |                       | 6    |                       | uV <sub>P-P</sub> |

|                 | Input voltage noise density       | f = 10 KHz                                                    |                       | 27   |                       |                   |

| en              | Input current noise density       | f = 1 KHz                                                     |                       | 29   |                       | – nV/√Hz          |

| In              | Input current noise density       | f = 1 KHz                                                     |                       | 10   |                       | fA/√Hz            |

| INPUT VO        | DLTAGE                            |                                                               |                       |      |                       |                   |

| V <sub>CM</sub> | Common-mode voltage range         |                                                               | V <sub>S-</sub> – 0.1 |      | V <sub>S-</sub> + 0.1 | V                 |

|                 |                                   | V <sub>S</sub> = 5.5 V, V <sub>CM</sub> = −0.1 to 5.6 V       | 80                    | 96   |                       |                   |

|                 |                                   | $V_{CM} = 0$ to 5.3 V, $T_{A} = -40$ to                       | 70                    |      |                       | -                 |

| CMRR            | Common-mode rejection ratio       | +125°C                                                        | 70                    |      |                       | - dB              |

| CINIKK          |                                   | $V_{\rm S}$ = 2.0 V, $V_{\rm CM}$ = -0.1 to 2.1 V             | 74                    | 88   |                       |                   |

|                 |                                   | $V_{CM} = 0$ to 1.8 V, $T_A = -40$ to                         | 65                    |      |                       |                   |

|                 |                                   | +125°C                                                        | 00                    |      |                       |                   |

| INPUT IM        | PEDANCE                           |                                                               |                       |      |                       | -                 |

| CIN             | Input capacitance                 | Differential                                                  |                       | 2.0  |                       | pF                |

| ON              | input oupdonance                  | Common mode                                                   |                       | 3.5  |                       | Pi                |

| OPEN-LC         | OOP GAIN                          |                                                               |                       |      |                       |                   |

|                 |                                   | $R_L$ = 10 kΩ, $V_O$ = 0.05 to 3.5 V                          | 90                    | 105  |                       |                   |

| Avol            | Open leen veltage gein            | T <sub>A</sub> = −40 to +125°C                                | 85                    |      |                       | dD                |

| AVOL            | Open-loop voltage gain            | $R_L$ = 600 $\Omega,V_O$ = 0.15 to 3.5 V                      | 85                    | 100  |                       | – dB<br>–         |

|                 |                                   | T <sub>A</sub> = −40 to +125°C                                | 80                    |      |                       |                   |

| FREQUE          | NCY RESPONSE                      |                                                               |                       |      |                       |                   |

| GBW             | Gain band width product           |                                                               |                       | 1    |                       | MHz               |

| SR              | Slew rate                         | G = +1, CL= 100pF,                                            |                       | 1    |                       | V/ue              |

| SR              | Slew rate                         | Vo= 1.5 to 3.5 V                                              |                       | 1    |                       | V/µs              |

# **Electrical Characteristics**

$V_S = 5.0 \text{ V}, V_{CM} = V_S / 2, V_O = V_S / 2$ , and  $R_L = 10 k\Omega$  connected to  $V_S / 2, T_A = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply over the specified temperature range,  $T_A = -40$  to +125 °C.

| SYMBOL          | PARAMETER                         | CONDITIONS                                             | MIN TYP                                   | MAX                  | UNIT |  |

|-----------------|-----------------------------------|--------------------------------------------------------|-------------------------------------------|----------------------|------|--|

| THD+N           | Total harmonic distortion + noise | G = +1, f = 1 KHz, V <sub>O</sub> = 1 V <sub>RMS</sub> | 0.002                                     |                      | %    |  |

| 4               | Sottling time                     | To 0.1%, G = +1, 1V step                               | 1.2                                       |                      |      |  |

| ts              | Settling time                     | To 0.01%, G = +1, 1V step                              | 1.5                                       |                      | μs   |  |

| t <sub>OR</sub> | Overload recovery time            | To 0.1%, V <sub>IN</sub> * Gain > V <sub>S</sub>       | 2                                         |                      | μs   |  |

| OUTPUT          |                                   |                                                        | ·                                         |                      |      |  |

| Vон             | High output voltage swing         | R <sub>L</sub> = 10 kΩ                                 | V <sub>S+</sub> - 19 V <sub>S+</sub> - 11 |                      | mV   |  |

| Vol             | Low output voltage swing          | R <sub>L</sub> = 10 kΩ                                 | V <sub>S-</sub> + 8                       | V <sub>S-</sub> + 14 | mV   |  |

| lsc             | Short-circuit current             |                                                        | ±45                                       |                      | mA   |  |

| POWER \$        | SUPPLY                            |                                                        |                                           |                      |      |  |

| M               |                                   | $T_A = 0^{\circ}C$ to +70°C                            | 1.8                                       | 5.5                  | N    |  |

| Vs              | Operating supply voltage          | T <sub>A</sub> = −40°C to +125°C                       | 2.0                                       | 5.5                  |      |  |

|                 | Quiescent current (per            |                                                        | 85                                        | 135                  |      |  |

| lq              | amplifier)                        | T <sub>A</sub> = -40°C to +125°C                       |                                           | 170                  | μA   |  |

1. Guaranteed by design and engineering sample characterization.

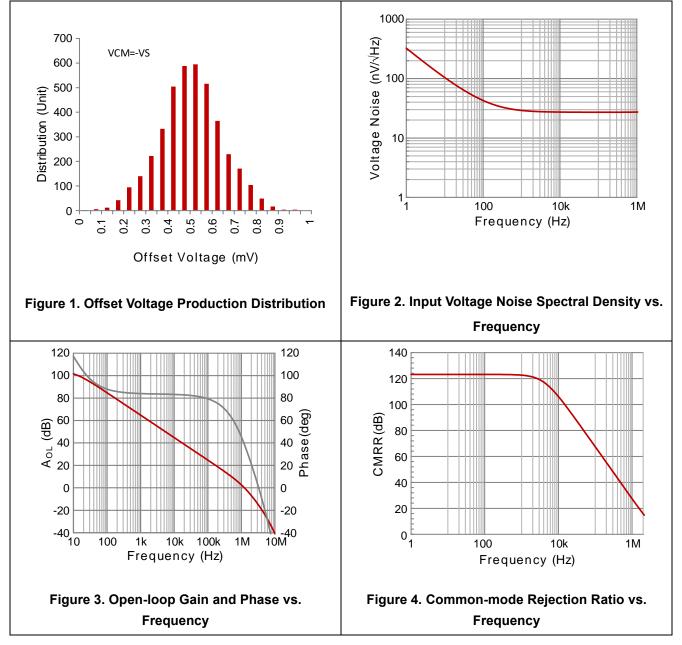

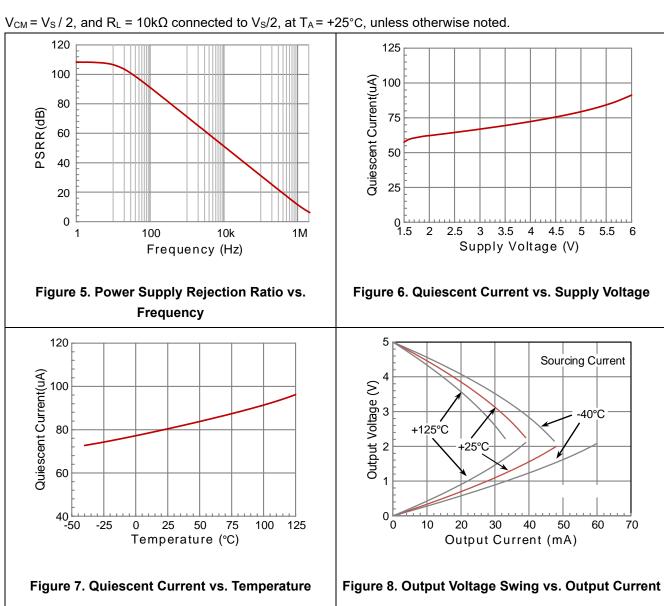

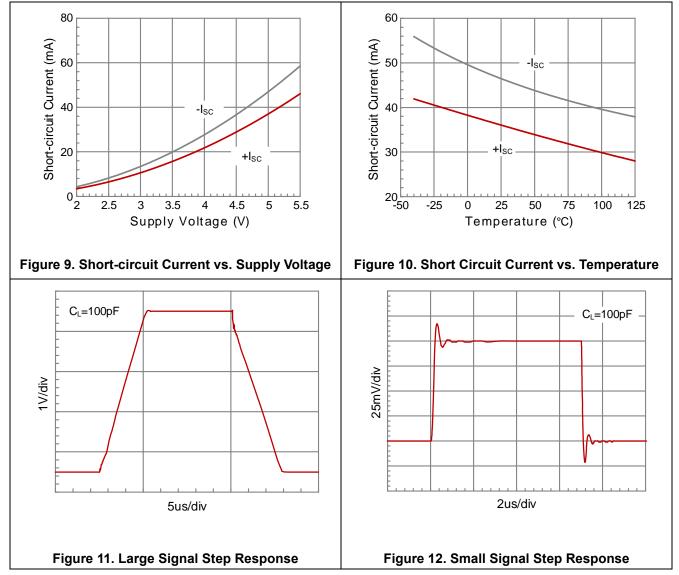

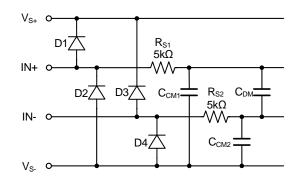

## 5.6 Typical Characteristics

$V_{CM}$  =  $V_S/$  2, and  $R_L$  = 10k $\Omega$  connected to  $V_S/2,$  at  $T_A$  = +25°C, unless otherwise noted.

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

# 6 Functional Description

The GD30AP321A and GD30AP358A is a family of low-power, rail-to-rail input and output operational amplifiers specifically designed for portable applications. These devices operate from 1.8V to 5.5V at the temperature range of 0°C to 70°C, are unity-gain stable, and suitable for a wide range of general-purpose applications. The class AB output stage is capable of driving  $\leq 10k\Omega$  loads connected to any point between V<sub>S+</sub> and ground. The input common-mode voltage range includes both rails, and allows the GD30AP321A and GD30AP358A family to be used in virtually any single-supply application. Rail-to-rail input and output swing significantly increases dynamic range, especially in low-supply applications, and makes them ideal for driving sampling analog-to-digital converters (ADCs).

The GD30AP321A and GD30AP358A features 1MHz bandwidth and 1V/µs slew rate with only 85µA supply current per amplifier, providing good ac performance at very low power consumption. DC applications are also well served with a low input noise voltage of  $29nV/\sqrt{Hz}$  at 1kHz, low input bias current, and an input offset voltage of 1.0mV maximally. The typical offset voltage drift is  $1µV/^{\circ}C$ , over the full temperature range the input offset voltage changes only 100µV (0.5mV to 0.6mV).

## 6.1 Operating Voltage

The GD30AP321A and GD30AP358A family is optimized for operation at voltages as low as +1.8V ( $\pm$ 0.9V) and up to +5.5V ( $\pm$ 2.75V) at the temperature range of 0°C to 70°C, and fully specified and ensured for operation from 2.0V to 5.5V ( $\pm$ 1.0V to  $\pm$ 2.75V). In addition, many specifications apply from -40°C to +125°C. Parameters that vary significantly with operating voltages or temperature are illustrated in the *Typical Characteristics* graphs.

**NOTE:** Supply voltages ( $V_{S+}$  to  $V_{S-}$ ) higher than +10 V can permanently damage the device.

### 6.2 Rail-to-Rail Input

The input common-mode voltage range of the GD30AP321A and GD30AP358A series extends 100mV beyond the negative and positive supply rails. This performance is achieved with a complementary input stage: an N-channel input differential pair in parallel with a P-channel differential pair. The N-channel pair is active for input voltages close to the positive rail, typically  $V_{S+}-1.4V$  to the positive supply, whereas the P-channel pair is active for input for inputs from 100mV below the negative supply to approximately  $V_{S+}-1.4V$ . There is a small transition region, typically  $V_{S+}-1.2V$  to  $V_{S+}-1V$ , in which both pairs are on. This 200mV transition region can vary up to 200mV with process variation. Thus, the transition region (both stages on) can range from  $V_{S+}-1.4V$  to  $V_{S+}-1.2V$  on the low end, up to  $V_{S+}-1V$  to  $V_{S+}-0.8V$  on the high end. Within this transition region, PSRR, CMRR, offset voltage, offset drift, and THD can be degraded compared to device operation outside this region.

The typical input bias current of the GD30AP321A and GD30AP358A during normal operation is approximately 1pA. In overdriven conditions, the bias current can increase significantly. The most common cause of an overdriven condition occurs when the operational amplifier is outside of the linear range of operation. When the output of the operational amplifier is driven to one of the supply rails, the feedback loop requirements cannot be satisfied and a differential input voltage develops across the input pins. This differential input voltage results in activation of parasitic diodes inside the front-end input chopping switches that combine with electromagnetic interference (EMI) filter resistors to create the equivalent circuit. Notice that the input bias current remains within specification in the linear region.

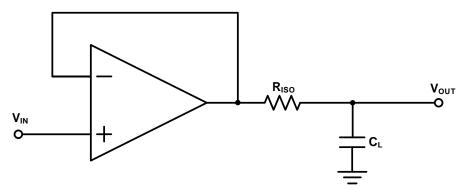

#### 6.3 Input EMI Filter and Clamp Circuit

Figure 13 shows the input EMI filter and clamp circuit. The GD30AP321A and GD30AP358A op-amps have internal ESD protection diodes (D1, D2, D3, and D4) that are connected between the inputs and each supply rail. These diodes protect the input transistors in the event of electrostatic discharge and are reverse biased during normal operation. This protection scheme allows voltages as high as approximately 500mV beyond the rails to be applied at the input of either terminal without causing permanent damage. These ESD protection current-steering diodes also provide in-circuit, input overdrive protection, as long as the current is limited to 20mA as stated in the *Absolute Maximum Ratings*.

Operational amplifiers vary in susceptibility to EMI. If conducted EMI enters the operational amplifier, the dc offset at the amplifier output can shift from its nominal value when EMI is present. This shift is a result of signal rectification associated with the internal semiconductor junctions. Although all operational amplifier pin functions can be affected by EMI, the input pins are likely to be the most susceptible. The EMI filter of these amplifiers is composed of two  $5k\Omega$  input series resistors (R<sub>S1</sub> and R<sub>S2</sub>), two common-mode capacitors (C<sub>CM1</sub> and C<sub>CM2</sub>), and a differential capacitor (C<sub>DM</sub>). These RC networks set the –3dB low-pass cutoff frequencies at 35MHz for commonmode signals, and at 22MHz for differential signals.

#### 6.4 Rail-to-Rail Output

Designed as a micro-power, low-noise operational amplifier, the GD30AP321A / GD30AP358A delivers a robust output drive capability. A class AB output stage with common- source transistors is used to achieve full rail-to-rail output swing capability. For resistive loads up to  $100k\Omega$ , the output swings typically to within 5mV of either supply rail regardless of the power-supply voltage applied. Different load conditions change the ability of the amplifier to swing close to the rails. For resistive loads up to  $10k\Omega$ , the output swings typically to within 11mV of the positive supply rail and within 8mV of the negative supply rail.

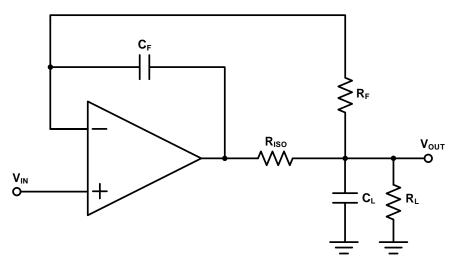

### 6.5 Capacitive Load and Stability

The GD30AP321A / GD30AP358A family can safely drive capacitive loads of up to 500pF in any configuration. As with most amplifiers, driving larger capacitive loads than specified may cause excessive overshoot and ringing, or even oscillation. A heavy capacitive load reduces the phase margin and causes the amplifier frequency response to peak. Peaking corresponds to over-shooting or ringing in the time domain. Therefore, it is recommended that external compensation be used if the GD30AP321A / GD30AP358A op-amps must drive a load exceeding 500pF. This compensation is particularly important in the unity-gain configuration, which is the worst case for stability.

www.gigadevice.com

A quick and easy way to stabilize the op-amp for capacitive load drive is by adding a series resistor,  $R_{ISO}$ , between the amplifier output terminal and the load capacitance, as shown in Figure 14.  $R_{ISO}$  isolates the amplifier output and feedback network from the capacitive load. The bigger the  $R_{ISO}$  resistor value, the more stable  $V_{OUT}$  will be. Note that this method results in a loss of gain accuracy because  $R_{ISO}$  forms a voltage divider with the  $R_L$ .

Figure 14. Indirectly Driving Heavy Capacitive Load

An improvement circuit is shown in Figure 15. It provides DC accuracy as well as AC stability. The  $R_F$  provides the DC accuracy by connecting the inverting signal with the output.

The C<sub>F</sub> and R<sub>ISO</sub> serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop.

For no-buffer configuration, there are two others ways to increase the phase margin: (a) by increasing the amplifier's gain, or (b) by placing a capacitor in parallel with the feedback resistor to counteract the parasitic capacitance associated with inverting node.

Figure 15. Indirectly Driving Heavy Capacitive Load with DC Accuracy

### 6.6 Overload Recovery

Overload recovery is defined as the time required for the operational amplifier output to recover from a saturated state to a linear state. The output devices of the operational amplifier enter a saturation region when the output voltage exceeds the rated operating voltage, either because of the high input voltage or the high gain. After the device enters the saturation region, the charge carriers in the output devices require time to return back to the

linear state. After the charge carriers return back to the linear state, the device begins to slew at the specified slew rate. Thus, the propagation delay in case of an overload condition is the sum of the overload recovery time and the slew time. The overload recovery time for the GD30AP321A / GD30AP358A family is approximately 2µs.

### 6.7 EMI Rejection Ratio

Circuit performance is often adversely affected by high frequency EMI. When the signal strength is low and transmission lines are long, an op-amp must accurately amplify the input signals. However, all op-amp pins — the non-inverting input, inverting input, positive supply, negative supply, and output pins — are susceptible to EMI signals. These high frequency signals are coupled into an op-amp by various means, such as conduction, near field radiation, or far field radiation. For example, wires and printed circuit board (PCB) traces can act as antennas and pick up high frequency EMI signals.

Amplifiers do not amplify EMI or RF signals due to their relatively low bandwidth. However, due to the nonlinearities of the input devices, op-amps can rectify these out of band signals. When these high frequency signals are rectified, they appear as a dc offset at the output.

The GD30AP321A / GD30AP358A op-amps have integrated EMI filters at their input stage. A mathematical method of measuring EMIRR is defined as follows:

$$\mathsf{EMIRR} = 20 \times \mathsf{log} \left( \frac{\mathsf{V}_{\mathsf{IN\_PEAK}}}{\Delta \mathsf{V}_{\mathsf{OS}}} \right) \tag{1}$$

### 6.8 Input-to-Output Coupling

To minimize capacitive coupling, the input and output signal traces should not be parallel. This helps reduce unwanted positive feedback.

### 6.9 Maximizing Performance Through Proper Layout

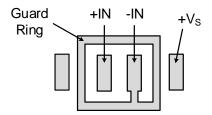

To achieve the maximum performance of the extremely high input impedance and low offset voltage of the GD30AP321A / GD30AP358A op-amps, care is needed in laying out the circuit board. The PCB surface must remain clean and free of moisture to avoid leakage currents between adjacent traces. Surface coating of the circuit board reduces surface moisture and provides a humidity barrier, reducing parasitic resistance on the board. The use of guard rings around the amplifier inputs further reduces leakage currents. Figure 16 shows proper guard ring configuration and the top view of a surface-mount layout. The guard ring does not need to be a specific width, but it should form a continuous loop around both inputs. By setting the guard ring voltage equal to the voltage at the non-inverting input, parasitic capacitance is minimized as well. For further reduction of leakage currents, components can be mounted to the PCB using Teflon standoff insulators.

Figure 16. Use a Guard Ring around Sensitive Pins

www.gigadevice.com

Other potential sources of offset error are thermoelectric voltages on the circuit board. This voltage, also called Seebeck voltage, occurs at the junction of two dissimilar metals and is proportional to the temperature of the junction. The most common metallic junctions on a circuit board are solder-to-board trace and solder-to-component lead. If the temperature of the PCB at one end of the component is different from the temperature at the other end, the resulting Seebeck voltages are not equal, resulting in a thermal voltage error.

This thermocouple error can be reduced by using dummy components to match the thermoelectric error source. Placing the dummy component as close as possible to its partner ensures both Seebeck voltages are equal, thus canceling the thermocouple error. Maintaining a constant ambient temperature on the circuit board further reduces this error. The use of a ground plane helps distribute heat throughout the board and reduces EMI noise pickup.

# 7 Application Information

#### 7.1 Typical Application Circuit

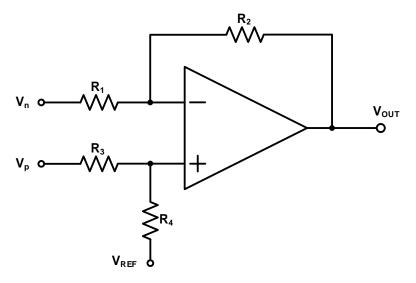

#### 7.1.1 Differential Amplifier

The circuit shown in Figure 17 performs the difference function. If the resistors ratios are equal R4/R3 = R2/R1, then:

$$V_{OUT} = (V_{P} - V_{N}) \times \frac{R_{2}}{R_{1}} + V_{REF}$$

<sup>(2)</sup>

Figure 17. Differential Amplifier

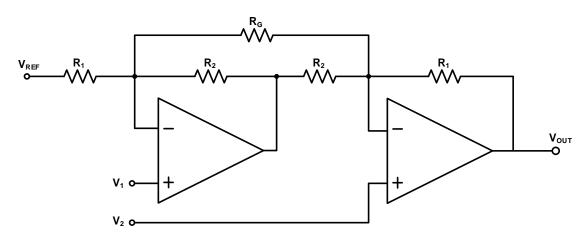

#### 7.1.2 Instrumentation Amplifier

**Figure 18. Instrumentation Amplifier**

The GD30AP321A / GD30AP358A family is well suited for conditioning sensor signals in battery-powered applications. Figure 18 shows a two op-amp instrumentation amplifier, using the GD30AP321A / GD30AP358A op-amps. The circuit works well for applications requiring rejection of common-mode noise at higher gains. The reference voltage ( $V_{REF}$ ) is supplied by a low-impedance source. In single voltage supply applications, the  $V_{REF}$  is

typically Vs/2.

$$V_{OUT} = (V_2 - V_1) \times \left(1 + \frac{R_1}{R_2} + \frac{2R_1}{R_G}\right) + V_{REF}$$

(3)

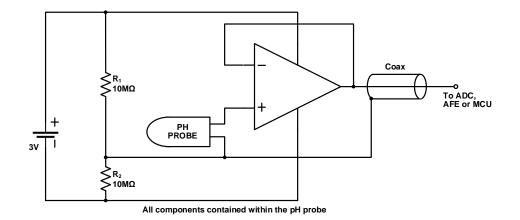

#### 7.1.3 Buffered Chemical Sensors

#### Figure 19. Buffered pH Probe

The GD30AP321A / GD30AP358A family has input bias current in the pA range. This is ideal in buffering high impedance chemical sensors, such as pH probes. As an example, the circuit in Figure 19 eliminates expansive low-leakage cables that is required to connect a pH probe (general purpose combination pH probes, e.g Corning 476540) to metering ICs such as ADC, AFE and/or MCU. A GD30AP321A / GD30AP358A op-amp and a lithium battery are housed in the probe assembly. A conventional low-cost coaxial cable can be used to carry the op-amp's output signal to subsequent ICs for pH reading.

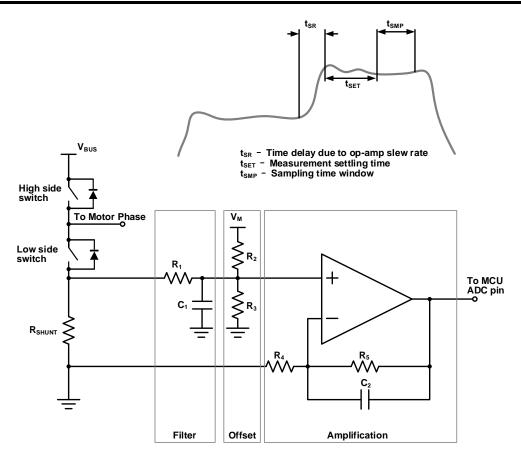

#### 7.1.4 Motor Phase Current Sensing

The current sensing amplification shown in Figure 20 has a slew rate of  $2\pi$  fV<sub>PP</sub> for the output of sine wave signal, and has a slew rate of 2fV<sub>PP</sub> for the output of triangular wave signal. In most of motor control systems, the PWM frequency is at 10KHz to 20KHz, and one cycle time is 100µs for a 10KHz of PWM frequency. In current shunt monitoring for a motor phase, the phase current is converted to a phase voltage signal for ADC sampling. This sampling voltage signal must be settled before entering the ADC. As the Figure 20 shown, the total settling time of a current shunt monitor circuit includes: the rising edge delay time (t<sub>SR</sub>) due to the op-amp's slew rate, and the measurement settling time (t<sub>SET</sub>). For a 3-shunt solution in motor phase current sensing, if the smaller duty cycle of the PWM is defined at 45% (In fact, the phase with minimum PWM duty cycle, such as 5%, is not detected current directly, and it can be calculated from the other two phase currents), and the t<sub>SR</sub> is required at 20% of a total time window for a phase current monitoring, in case of a 3.3 V motor control system (3.3 V MCU with 12-bit ADC), the op-amp's slew rate should be more than:

$$\frac{3.3V}{100us \times 45\% \times 20\%} = 0.37V / us$$

(4)

At the same time, the op-amp's bandwidth should be much greater than the PWM frequency, like 10 time at least.

Figure 20. Current Shunt Monitor Circuit

# 8 Package Information

## 8.1 Outline Dimensions

- 1. All dimensions are in millimeters.

- 2. Package dimensions does not include mold flash, protrusions, or gate burrs.

- 3. Refer to the Table 1. SOT23-5L dimensions(mm).

#### Table 1. SOT23-5L dimensions(mm)

| SYMBOL | MIN  | ТҮР      | МАХ  |

|--------|------|----------|------|

| A      |      |          | 1.25 |

| A1     | 0.04 |          | 0.1  |

| A2     | 1.00 |          | 1.20 |

| b      | 0.33 |          | 0.41 |

| С      | 0.15 |          | 0.19 |

| D      | 2.82 |          | 3.02 |

| E      | 2.60 |          | 3.00 |

| E1     | 1.5  |          | 1.7  |

| e      |      | 0.95 BSC |      |

| e1     |      | 1.90 BSC |      |

| L      |      | 0.60 REF |      |

| L1     | 0.30 |          | 0.60 |

| θ      | 0°   |          | 8°   |

1. Refer to the Table 2. SOIC-8L dimensions(mm).

#### Table 2. SOIC-8L dimensions(mm)

| SYMBOL | MIN   | ТҮР   | MAX   |

|--------|-------|-------|-------|

| A      | 1.37  |       | 1.67  |

| A1     | 0.07  |       | 0.17  |

| A2     | 1.3   |       | 1.5   |

| b      | 0.306 |       | 0.506 |

| С      |       | 0.203 |       |

| D      | 4.7   |       | 5.1   |

| E      | 3.82  |       | 4.02  |

| E1     | 5.8   |       | 6.2   |

| e      |       | 1.27  |       |

| L      | 0.45  |       | 0.75  |

| θ      | 0°    |       | 8°    |

1. Refer to the Table 3. *MSOP-8L dimensions(mm)*.

#### Table 3. MSOP-8L dimensions(mm)

| SYMBOL | MIN  | ТҮР  | MAX  |

|--------|------|------|------|

| A      | 0.80 |      | 1.10 |

| A1     | 0.05 |      | 0.15 |

| A2     | 0.75 |      | 0.95 |

| b      | 0.29 |      | 0.38 |

| С      | 0.15 |      | 0.20 |

| D      | 2.90 |      | 3.10 |

| E      | 2.90 |      | 3.10 |

| E1     | 4.70 |      | 5.10 |

| е      |      | 0.65 |      |

| L      | 0.40 |      | 0.70 |

| θ      | 0°   |      | 8°   |

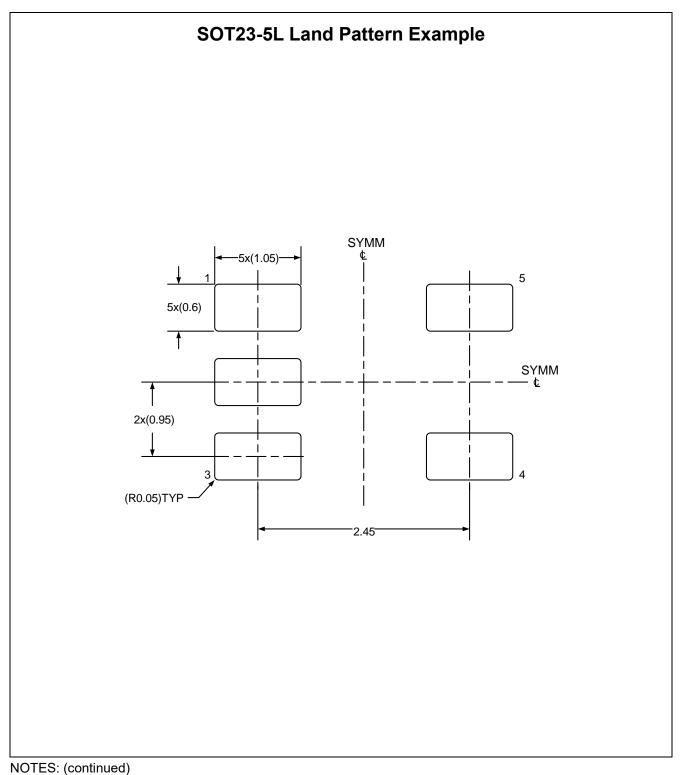

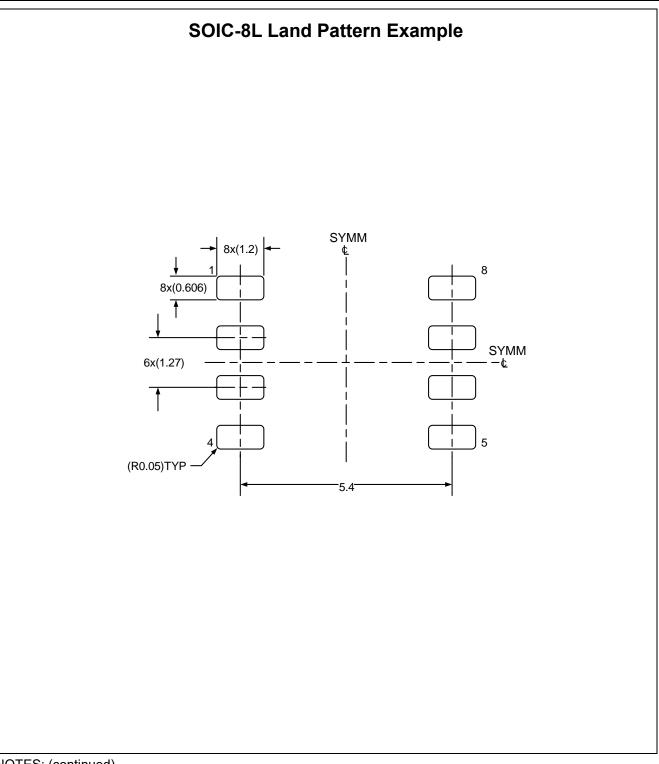

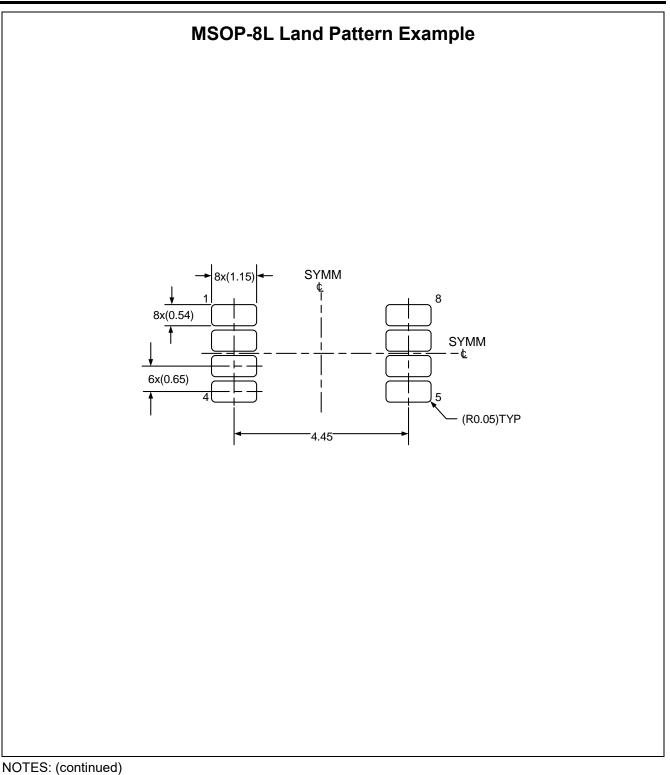

### 8.2 Recommended Land Pattern

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 20X scale.

NOTES: (continued)

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 20X scale.

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 20X scale.

# 9 Ordering Information

| Ordering Code      | Package Type | ECO Plan | Packing Type | MOQ  | OP Temp(°C)     |

|--------------------|--------------|----------|--------------|------|-----------------|

| GD30AP321ANSTR-I01 | SOT23-5L     | Green    | Tape & Reel  | 3000 | −40°C to +125°C |

| GD30AP358AWLTR-I02 | SOIC-8L      | Green    | Tape & Reel  | 4000 | -40°C to +125°C |

| GD30AP358AWMTR-I02 | MSOP-8L      | Green    | Tape & Reel  | 3000 | -40°C to +125°C |

# **10 Revision History**

| REVISION NUMBER | DESCRIPTION                        | DATE |

|-----------------|------------------------------------|------|

| 1.0             | Initial release and device details | 2024 |

## **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company according to the laws of the People's Republic of China and other applicable laws. The Company reserves all rights under such laws and no Intellectual Property Rights are transferred (either wholly or partially) or licensed by the Company (either expressly or impliedly) herein. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no representations or warranties of any kind, express or implied, with regard to the merchantability and the fitness for a particular purpose of the Product, nor does the Company assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the sole responsibility of the user of this document to determine whether the Product is suitable and fit for its applications and products planned, and properly design, program, and test the functionality and safety of its applications and products planned using the Product. Unless otherwise expressly specified in the datasheet of the Product, the Product is designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only, and the Product is not designed or intended for use in (i) safety critical applications such as weapons systems, nuclear facilities, atomic energy controller, combustion controller, aeronautic or aerospace applications, traffic signal instruments, pollution control or hazardous substance management; (ii) life-support systems, other medical equipment or systems (including life support equipment and surgical implants); (iii) automotive applications or environments, including but not limited to applications for active and passive safety of automobiles (regardless of front market or aftermarket), for example, EPS, braking, ADAS (camera/fusion), EMS, TCU, BMS, BSG, TPMS, Airbag, Suspension, DMS, ICMS, Domain, ESC, DCDC, e-clutch, advancedlighting, etc.. Automobile herein means a vehicle propelled by a self-contained motor, engine or the like, such as, without limitation, cars, trucks, motorcycles, electric cars, and other transportation devices; and/or (iv) other uses where the failure of the device or the Product can reasonably be expected to result in personal injury, death, or severe property or environmental damage (collectively "Unintended Uses"). Customers shall take any and all actions to ensure the Product meets the applicable laws and regulations. The Company is not liable for, in whole or in part, and customers shall hereby release the Company as well as its suppliers and/or distributors from, any claim, damage, or other liability arising from or related to all Unintended Uses of the Product. Customers shall indemnify and hold the Company, and its officers, employees, subsidiaries, affiliates as well as its suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Product.

Information in this document is provided solely in connection with the Product. The Company reserves the right to make changes, corrections, modifications or improvements to this document and the Product described herein at any time without notice. The Company shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 GigaDevice – All rights reserved