# General Purpose, 1.8V, RRI, Open-Drain Output Comparators

## 1 Features

- Micro-power Operating Current (37µA) Preserves Battery Power

- Fast 100ns Propagation Delay (100mV Overdrive)

- Single 1.8V to 5.5V Supply Voltage Range

- Can be Powered From the Same

1.8V/2.5V/3.3V/5V System Rails

- Rail-to-Rail Input

- Open-Drain Output Current Drive: 30mA Typically at 5V Supply

- Internal Hysteresis for Clean Switching

- Internal RF/EMI Filter

- Operating Temperature Range: -40°C to +125°C

## 2 Applications

- Consumer Accessories

- Portable and Battery-Powered Devices

- Alarms and Monitoring Circuits

- Threshold Detectors and Discriminators

- Logic Level Shifting or Translation

- Zero-Crossing Detectors

- Window Comparators

- IR Receivers

- Line Receivers

## 3 Description

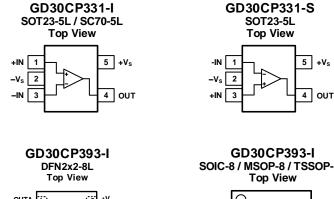

The GD30CP331/GD30CP393 single-/dualchannel comparator are drop-in, pin-for-pin compatible replacements for the GD30CP331/GD30CP393, and low-voltage versions of GD30CP331/GD30CP393. The devices with open-drain output offer the ultimate combination of high speed (100ns propagation delay) and very low power consumption (37 $\mu$ A), and feature such as rail-to- rail inputs, low offset voltage (typically 1mV), large output drive current, and a wide range of supply voltages from 1.8V to 5.5V. The devices are very easy to implement in a wide variety of applications where require critical response time, power-sensitive, low-voltage, and/or tight board space.

Advantages of the GD30CP331/GD30CP393 also include the added benefit of internal hysteresis provide noise immunity, preventing output oscillations even with slow-moving input signals. Designed with the most modern techniques, the GD30CP331/GD30CP393 achieve superior performance over BiCMOS or bipolar versions on the market.

The GD30CP331(single) is available in both SOT23-5L and SC70-5L packages. The GD30CP393 (dual) is offered in DFN-8L, SOIC-8L, MSOP-8L and TSSOP-8L packages. All devices are rated over -40°C to +125°C industrial temperature range.

| PART NUMBER | PACKAGE   | BODY SIZE (NOM) |  |  |  |  |

|-------------|-----------|-----------------|--|--|--|--|

| GD30CP331   | SOT23-5L  | 2.92mm x 1.63mm |  |  |  |  |

| GD30CP331   | SC70-5L   | 2.10mm x 1.25mm |  |  |  |  |

|             | DFN2x2-8L | 2.00mm x 2.00mm |  |  |  |  |

| 000000000   | SOIC-8L   | 4.90mm x 3.92mm |  |  |  |  |

| GD30CP393   | MSOP-8L   | 3.00mm x 3.00mm |  |  |  |  |

|             | TSSOP-8L  | 4.96mm x 4.40mm |  |  |  |  |

#### Device Information<sup>1</sup>

1. For all available packages, see the *Package Information* and *Ordering Information* at the end of datasheet.

# **Table of Contents**

| 1   | Featu                | res                                          | 1  |  |  |  |

|-----|----------------------|----------------------------------------------|----|--|--|--|

| 2   | Appli                | cations                                      | 1  |  |  |  |

| 3   | Descr                | iption                                       | 1  |  |  |  |

| Tab | le of C              | ontents                                      | 2  |  |  |  |

| 4   | Devic                | e Overview                                   | 3  |  |  |  |

|     | 4.1                  | Pinout and Pin Assignment                    | 3  |  |  |  |

|     | 4.2                  | Pin Description                              | 3  |  |  |  |

| 5   | Paran                | neter Information                            | 4  |  |  |  |

|     | 5.1                  | Absolute Maximum Ratings                     | 4  |  |  |  |

|     | 5.2                  | Recommended Operation Conditions             | 4  |  |  |  |

|     | 5.3                  | Electrical Sensitivity                       | 4  |  |  |  |

|     | 5.4                  | Thermal Characteristics                      | 4  |  |  |  |

|     | 5.5                  | Electrical Characteristics                   | 5  |  |  |  |

|     | 5.6                  | Typical Characteristics                      | 7  |  |  |  |

| 6   | Funct                | ional Description                            | 11 |  |  |  |

|     | 6.1                  | Operating Voltage                            | 11 |  |  |  |

|     | 6.2                  | Rail-to-Rail Input                           | 11 |  |  |  |

|     | 6.3                  | Input EMI Filter and Clamp Circuit           | 11 |  |  |  |

|     | 6.4                  | EMI Rejection Ration                         | 12 |  |  |  |

|     | 6.5                  | Internal Hysteresis                          | 12 |  |  |  |

|     | 6.6                  | Input-to-Output Coupling                     | 13 |  |  |  |

|     | 6.7                  | Maximizing Performance Through Proper Layout | 13 |  |  |  |

| 7   | Appli                | cation Information                           | 15 |  |  |  |

|     | 7.1                  | IR Receiver AFE and Wake Up Circuit          | 15 |  |  |  |

|     | 7.2                  | Window Comparator                            | 16 |  |  |  |

| 8   | Packa                | ge Information                               | 18 |  |  |  |

|     | 8.1                  | Outline Dimensions                           | 18 |  |  |  |

|     | 8.2                  | Recommended Land Pattern                     | 30 |  |  |  |

| 9   | Ordering Information |                                              |    |  |  |  |

| 10  | Revision History     |                                              |    |  |  |  |

## 4 Device Overview

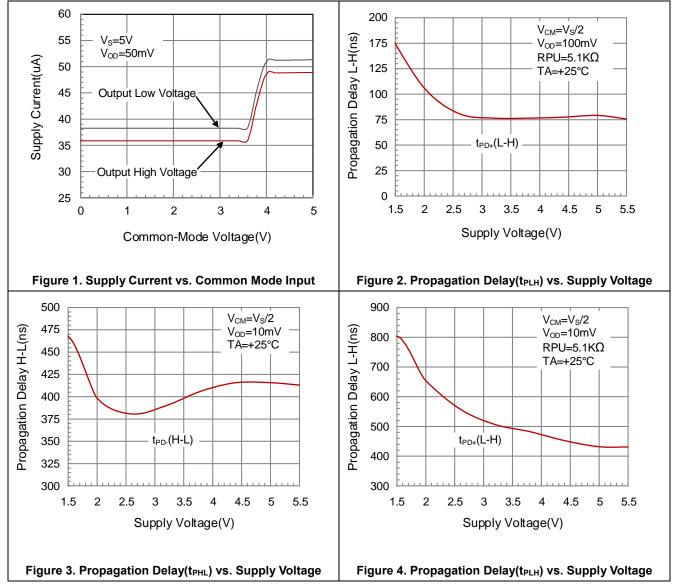

## 4.1 Pinout and Pin Assignment

## 4.2 Pin Description

| PIN NUMBER<br>NAME | PIN TYPE <sup>1</sup> | FUNCTION                                                            |  |

|--------------------|-----------------------|---------------------------------------------------------------------|--|

| -IN                | I                     | Negative input. The voltage range is from (VS 0.1V) to (VS+ + 0.1V) |  |

| +IN                | I                     | Positive input. This pin has the same voltage range as –IN.         |  |

| +V <sub>S</sub>    | Р                     | Positive power supply.                                              |  |

| -Vs                | Р                     | Negative power supply.                                              |  |

| OUT                | 0                     | Comparator output.                                                  |  |

1. I = Input, O = Output, P = Power.

# 5 Parameter Information

### 5.1 Absolute Maximum Ratings

Exceeding the operating temperature range (unless otherwise noted)<sup>1</sup>

| SYMBOL                             | PARAMETER                                   | MIN                   | MAX                   | UNIT |

|------------------------------------|---------------------------------------------|-----------------------|-----------------------|------|

| V <sub>S+</sub> to V <sub>S-</sub> | Supply Voltage, Vs+ to Vs-                  |                       | 10.0                  | V    |

| Vı                                 | Signal Input Voltage                        | V <sub>S-</sub> - 0.3 | V <sub>S+</sub> + 0.3 | V    |

| h                                  | Signal Input Current                        | -10                   | 10                    | mA   |

|                                    | Output Short-Circuit                        |                       | Continuous            | s    |

| TJ                                 | Junction Temperature, TJ                    |                       | 150                   | °C   |

| T <sub>stg</sub>                   | Storage Temperature Range, T <sub>stg</sub> | -65                   | +150                  | °C   |

|                                    | Lead Temperature Range (Soldering 10 sec)   |                       | 260                   | °C   |

The maximum ratings are the limits to which the device can be subjected without permanently damaging the device. Note that the device is not guaranteed to operate properly at the maximum ratings. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

## 5.2 Recommended Operation Conditions

| SYMBOL <sup>1,2</sup> | PARAMETER                   |                       | TYP MAX               | UNIT |

|-----------------------|-----------------------------|-----------------------|-----------------------|------|

| Vs                    | Input supply voltage range  | 1.8                   | 5.5                   | V    |

| V <sub>CM</sub>       | Common-mode voltage range   | V <sub>S-</sub> – 0.1 | V <sub>S+</sub> + 0.1 | V    |

| TA                    | Operating temperature range | -40                   | 125                   | °C   |

1. The device is not guaranteed to function outside of its operating conditions.

## 5.3 Electrical Sensitivity

| SYMBOL    | CONDITIONS                                                          | VALUE | UNIT |

|-----------|---------------------------------------------------------------------|-------|------|

| VESD(HBM) | Human-body model (HBM), ANSI/ESDA/JEDEC JS-001-2017 <sup>1</sup>    | ±5000 | V    |

| Vesd(CDM) | Charge-device model (CDM), ANSI/ESDA/JEDEC JS-002-2022 <sup>2</sup> | ±2000 | V    |

1. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

2. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 5.4 Thermal Characteristics

| SYMBOL <sup>1</sup> | CONDITIONS                 | PACKAGE   | VALUE | UNIT |

|---------------------|----------------------------|-----------|-------|------|

|                     | Package Thermal Resistance | SC70-5L   | 333   |      |

|                     |                            | SOT23-5L  | 190   |      |

|                     |                            | DFN2x2-8L | 94    | °C/W |

| Θ <sub>JA</sub>     |                            | MSOP-8L   | 201   |      |

|                     |                            | TSSOP-8L  | 160   |      |

|                     |                            | SOIC-8L   | 125   |      |

1. Thermal characteristics are based on simulation, and meet JEDEC document JESD51-7.

## 5.5 Electrical Characteristics

$V_s = 5.0 \text{ V}, V_{CM} = V_s /2, V_0 = V_s /2$ , and  $R_L = 10k\Omega$  connected to  $V_s /2, T_A = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply over the specified temperature range,  $T_A = -40$  to  $+125^{\circ}C$ .

| SYMBOL           | PARAMETER                         | CONDITIONS                                                            | MIN       | TYP | MAX       | UNIT      |  |

|------------------|-----------------------------------|-----------------------------------------------------------------------|-----------|-----|-----------|-----------|--|

| OFFSET           | VOLTAGE                           |                                                                       |           |     |           |           |  |

| Vos              | Input offset voltage              |                                                                       |           | ±1  | ±5        | mV        |  |

| dVos/d⊤          | Offset voltage drift <sup>1</sup> | T <sub>A</sub> = −40 to +125°C                                        |           | ±2  |           | µV/°C     |  |

|                  |                                   | V <sub>S</sub> = 1.8 to 5.5 V, V <sub>CM</sub> < V <sub>S+</sub> - 1V | 70        | 82  |           |           |  |

| PSRR             | Power supply rejection ratio      | T <sub>A</sub> = −40 to +125°C                                        | 66        |     |           | dB        |  |

| Hyst             | Input hysteresis                  | V <sub>CM</sub> = 0                                                   |           | 3   |           | mV        |  |

| INPUT BI         | AS CURRENT                        |                                                                       |           |     |           |           |  |

|                  |                                   | V <sub>CM</sub> = V <sub>S+</sub> / 2                                 |           | 5   | 30        |           |  |

| lв               | Input bias current <sup>1</sup>   | T <sub>A</sub> = −40 to +125°C                                        |           |     | 800       | pА        |  |

|                  |                                   | V <sub>CM</sub> = V <sub>S+</sub> / 2                                 |           | 10  | 50        |           |  |

| los              | Input offset current <sup>1</sup> | T <sub>A</sub> = −40 to +125°C                                        |           |     | 1000      | pА        |  |

|                  |                                   |                                                                       |           |     |           |           |  |

|                  |                                   | T <sub>A</sub> = −40 to +85°C                                         | Vs 0.1    |     | Vs₋ + 0.1 | - v       |  |

| Vcm              | Common-mode voltage range         | T <sub>A</sub> = −40 to +125°C                                        | Vs- + 0.1 |     | Vs₋ − 0.1 |           |  |

|                  | Common-mode rejection ratio       | V <sub>s</sub> = 5.5 V, V <sub>CM</sub> = −0.1 to 5.5 V               | 61        | 78  |           |           |  |

|                  |                                   | V <sub>CM</sub> = 0 to 5.3 V,                                         |           |     |           |           |  |

|                  |                                   | T <sub>A</sub> = −40 to +125°C                                        | 58        |     |           |           |  |

| CMRR             |                                   | Vs = 1.8 V, V <sub>CM</sub> = −0.1 to 1.8 V                           | 58        | 77  |           | – dB<br>– |  |

|                  |                                   | V <sub>CM</sub> = 0 to 1.6 V,                                         |           |     |           |           |  |

|                  |                                   | T <sub>A</sub> = −40 to+125°C                                         | 55        |     |           |           |  |

| INPUT IM         | PEDANCE                           |                                                                       |           |     |           |           |  |

| R <sub>IN</sub>  | Input resistance                  |                                                                       | 100       |     |           | GΩ        |  |

| 0                | 1                                 | Differential                                                          |           | 2.0 |           |           |  |

| CIN              | Input capacitance                 | Common mode                                                           |           | 3.5 |           | - pF      |  |

| SWITCHI          | NG CHARACTERISTICS                |                                                                       |           |     |           | 1         |  |

|                  |                                   | Input overdrive = 20mV,                                               |           | 040 |           |           |  |

| <b>+</b>         | Propagation delay time, High to   | C∟ = 15pF                                                             | 240       |     |           |           |  |

| t <sub>PD-</sub> | Low                               | Input overdrive = 100mV,                                              | 100       |     |           | ns        |  |

|                  |                                   | C <sub>L</sub> = 15pF                                                 |           |     |           |           |  |

|                  |                                   | Input overdrive = 20mV,                                               |           | 20  |           |           |  |

| t⊨               | Fall time                         | C∟ = 15pF                                                             |           | 20  |           | ns        |  |

| -                |                                   | Input overdrive = 100mV,                                              | 10        |     | 115       |           |  |

|                  |                                   | C <sub>L</sub> = 15pF                                                 |           |     |           |           |  |

## **Electrical Characteristics**

$V_S = 5.0 \text{ V}, V_{CM} = V_S / 2, V_O = V_S / 2$ , and  $R_L = 10 k\Omega$  connected to  $V_S / 2, T_A = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply over the specified temperature range,  $T_A = -40$  to +125 °C.

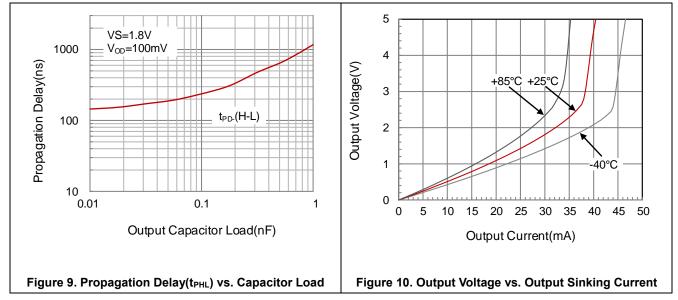

| SYMBOL          | PARAMETER                | CONDITIONS                                             | MIN | ТҮР | MAX | UNIT |

|-----------------|--------------------------|--------------------------------------------------------|-----|-----|-----|------|

| OUTPUT          | ОИТРИТ                   |                                                        |     |     |     |      |

| Vol             |                          | I <sub>SINK</sub> = 1mA                                |     | 50  | 80  | mV   |

| VOL             | Low output voltage swing | T <sub>A</sub> = −40 to +125°C                         |     |     | 90  | ΠV   |

| I <sub>SC</sub> | Short-circuit current    | Sink current                                           |     | -30 | -25 | mA   |

| POWER S         | SUPPLY                   |                                                        |     |     |     |      |

| Vs              | Operating supply voltage |                                                        | 1.8 |     | 5.5 | V    |

|                 |                          | Vs = 1.8V, V <sub>CM</sub> = 0.5V, I <sub>O</sub> = 0A |     | 32  | 40  |      |

| 1.              | Quiescent current (per   | T <sub>A</sub> = −40 to +125°C                         |     |     | 50  |      |

| la              | amplifier)               | Vs = 5.5V, V <sub>CM</sub> = 0.5V, I <sub>O</sub> = 0A |     | 37  | 45  | μA   |

|                 |                          | T <sub>A</sub> = −40 to +125°C                         |     |     | 60  |      |

1. Guaranteed by design and engineering sample characterization.

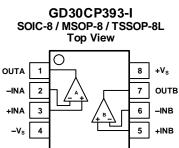

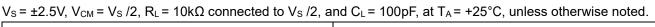

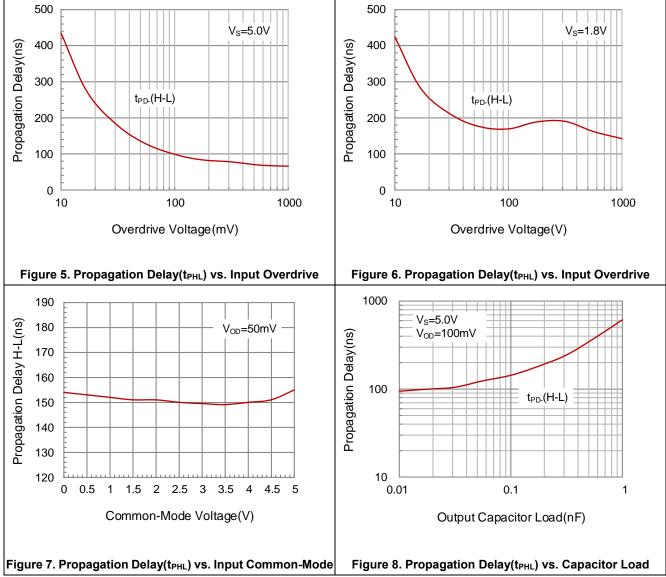

## 5.6 Typical Characteristics

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

$V_{s}$  = ±2.5V,  $V_{CM}$  =  $V_{s}$  /2,  $R_{L}$  = 10k $\Omega$  connected to  $V_{s}$  /2, and  $C_{L}$  = 100pF, at  $T_{A}$  = +25°C, unless otherwise noted.

## **Typical Characteristics (continued)**

# 6 Functional Description

## 6.1 Operating Voltage

The GD30CP331/GD30CP393 micro-power comparators of open-drain output are fully specified and ensured for operation from 1.8V to 5.5V and offers an excellent speed-to-power combination with a propagation delay of 100ns and a quiescent supply current of 37µA. This combination of fast response time at micro- power enables power conscious systems to monitor and respond quickly to fault conditions.

In addition, and many specifications apply over the industrial temperature range of -40 to +125°C. Parameters that vary significantly with operating voltages or temperature are illustrated in the Typical Characteristics graphs.

## 6.2 Rail-to-Rail Input

The input common-mode voltage range of the GD30CP331/GD30CP393 family extends 100mV beyond the supply rails. This performance is achieved with a complementary input stage: an N-channel input differential pair in parallel with a P-channel differential pair. The N-channel pair is active for input voltages close to the positive rail, typically  $V_{s+}$ -1.4V to the positive supply, whereas the P-channel pair is active for inputs from 100mV below the negative supply to approximately  $V_{s+}$ -1.4V. There is a small transition region, typically  $V_{s+}$ -1.2V to  $V_{s+}$ -1V, in which both pairs are on. This 200mV transition region can vary up to 200mV with process variation. Thus, the transition region (both stages on) can range from  $V_{s+}$ -1.4V to  $V_{s+}$ -1.2V on the low end, up to  $V_{s+}$ -1V to  $V_{s+}$ -0.8V on the high end. Within this transition region, PSRR, CMRR, offset voltage, offset drift, and THD can be degraded compared to device operation outside this region.

## 6.3 Input EMI Filter and Clamp Circuit

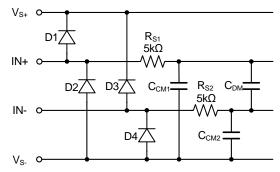

Figure 13 shows the input EMI filter and clamp circuit. The GD30CP331/GD30CP393 op-amps have internal ESD protection diodes (D1, D2, D3, and D4) that are connected between the inputs and each supply rail. These diodes protect the input transistors in the event of electrostatic discharge and are reverse biased during normal operation. This protection scheme allows voltages as high as approximately 500mV beyond the rails to be applied at the input of either terminal without causing permanent damage. See the table of Absolute Maximum Ratings for more information.

Figure 13. Input EMI Filter and Clamp Circuit

Operational amplifiers vary in susceptibility to EMI. If conducted EMI enters the operational amplifier, the dc offset at the amplifier output can shift from its nominal value when EMI is present. This shift is a result of signal rectification associated with the internal semiconductor junctions. Although all operational amplifier pin functions can be affected by EMI, the input pins are likely to be the most susceptible. The EMI filter of the

GD30CP331/GD30CP393 family is composed of two  $5k\Omega$  input series resistors (R<sub>S1</sub> and R<sub>S2</sub>), two common-mode capacitors (C<sub>CM1</sub> and C<sub>CM2</sub>), and a differential capacitor (C<sub>DM</sub>). These RC networks set the -3dB low-pass cutoff frequencies at 35MHz for common-mode signals, and at 22MHz for differential signals.

### 6.4 EMI Rejection Ration

Circuit performance is often adversely affected by high frequency EMI. When the signal strength is low and transmission lines are long, an amplifier must accurately amplify the input signals. However, all comparator pins — the non-inverting input, inverting input, positive supply, negative supply, and output pins — are susceptible to EMI signals. These high frequency signals are coupled into an comparator by various means, such as conduction, near field radiation, or far field radiation. For example, wires and printed circuit board (PCB) traces can act as antennas and pick up high frequency EMI signals.

Amplifiers do not amplify EMI or RF signals due to their relatively low bandwidth. However, due to the nonlinearities of the input devices, comparators can rectify these out of band signals. When these high frequency signals are rectified, they appear as a dc offset at the output.

The GD30CP331/GD30CP393 comparators have integrated EMI filters at their input stage. A mathematical method of measuring EMIRR is defined as follows:

$$\mathsf{EMIRR} = 20 \times \mathsf{log} \left( \frac{\mathsf{V}_{\mathsf{IN}\_\mathsf{PEAK}}}{\Delta \mathsf{V}_{\mathsf{OS}}} \right) \tag{1}$$

## 6.5 Internal Hysteresis

Most high-speed comparators oscillate in the linear region because of noise or undesired parasitic feedback. This tends to occur when the voltage on one input is at or equal to the voltage on the other input. To counter the parasitic effects and noise, the devices have an internal hysteresis of 3mV.

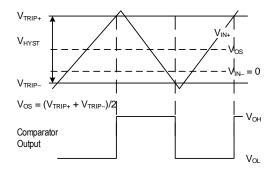

The hysteresis in a comparator creates two trip points: one for the rising input voltage and one for the falling input voltage. The difference between the trip points is the hysteresis. The average of the trip points is the offset voltage. When the comparator's input voltages are equal, the hysteresis effectively causes one comparator input voltage to move quickly past the other, thus taking the input out of the region where oscillation occurs. Standard comparators require hysteresis to be added with external resistors. To increase hysteresis and noise margin even more, add positive feedback with two resistors as a voltage divider from the output to the non-inverting input. Figure 14 illustrates the case where IN– is fixed and IN+ is varied. If the inputs were reversed, the figure would look the same, except the output would be inverted.

#### Figure 14. Input and Output Waveform, Non-inverting Input Varied

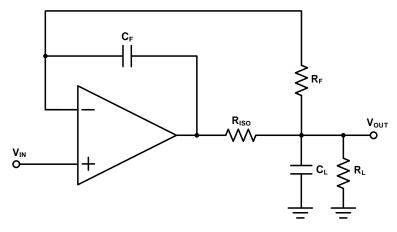

An improvement circuit is shown in Figure 15. It provides DC accuracy as well as AC stability. The R<sub>F</sub> provides the DC accuracy by connecting the inverting signal with the output.

The C<sub>F</sub> and R<sub>ISO</sub> serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop.

For no-buffer configuration, there are two others ways to increase the phase margin: (a) by increasing the amplifier's gain, or (b) by placing a capacitor in parallel with the feedback resistor to counteract the parasitic capacitance associated with inverting node.

Figure 15. Indirectly Driving Heavy Capacitive Load with DC Accuracy

### 6.6 Input-to-Output Coupling

To minimize capacitive coupling, the input and output signal traces should not be parallel. This helps reduce unwanted positive feedback.

## 6.7 Maximizing Performance Through Proper Layout

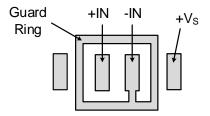

To achieve the maximum performance of the extremely high input impedance and low offset voltage of the GD30CP331/GD30CP393 op-amps, care is needed in laying out the circuit board. The PCB surface must remain clean and free of moisture to avoid leakage currents between adjacent traces. Surface coating of the circuit board reduces surface moisture and provides a humidity barrier, reducing parasitic resistance on the board. The use of guard rings around the amplifier inputs further reduces leakage currents. Figure 16 shows proper guard ring configuration and the top view of a surface-mount layout. The guard ring does not need to be a specific width, but it should form a continuous loop around both inputs. By setting the guard ring voltage equal to the voltage at the non-inverting input, parasitic capacitance is minimized as well. For further reduction of leakage currents, components can be mounted to the PCB using Teflon standoff insulators.

Figure 16. Use a Guard Ring around Sensitive Pins

Other potential sources of offset error are thermoelectric voltages on the circuit board. This voltage, also called Seebeck voltage, occurs at the junction of two dissimilar metals and is proportional to the temperature of the junction. The most common metallic junctions on a circuit board are solder-to-board trace and solder-to-component lead. If the temperature of the PCB at one end of the component is different from the temperature at the other end, the resulting Seebeck voltages are not equal, resulting in a thermal voltage error.

This thermocouple error can be reduced by using dummy components to match the thermoelectric error source. Placing the dummy component as close as possible to its partner ensures both Seebeck voltages are equal, thus canceling the thermocouple error. Maintaining a constant ambient temperature on the circuit board further reduces this error. The use of a ground plane helps distribute heat throughout the board and reduces EMI noise pickup.

# 7 Application Information

## 7.1 IR Receiver AFE and Wake Up Circuit

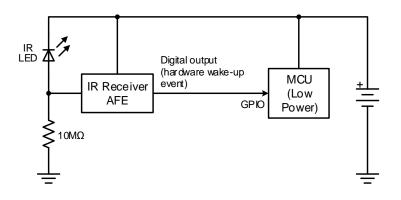

Infrared (IR) communication is inherently immune to RF interference as long as there is a line-of-sight path between the transmitter and the receiver. It is also one of the lowest cost communication schemes. This makes it a good choice for implementing wireless communications in applications such as utility metering. A common system topology to extend battery life is to use a power efficient IR receiver analog front end (AFE) that is always on and wakes up the host only when there is a valid IR signal detected as shown in Figure 17.

Figure 17. Low-Side Current Sensing Circiut

Any unused channel of the GD30CP331/GD30CP393 must be configured in unity gain with the input commonmode voltage tied to the midpoint of the power supplies.

Power efficient comparators such as the GD30CP331/GD30CP393 can be used in the IR receiver AFE to increase battery life. The GD30CP331/GD30CP393 device is responsible for two major tasks:

- IR signal conditioning

- Host system wake-up

The GD30CP331/GD30CP393 device is constantly powered to always be ready to receive IR signals and wake up the host microcontroller (MCU) when data is received. The short working distance (approx 5 cm) is suitable for a virtual-contact operation where the IR transmitter and receiver are closely placed with an optional mechanical alignment guide.

Figure 17 shows the IR receiver system block diagram. The host MCU is normally in the shutdown mode (during which the quiescent current is less than 1µA) except when data is being transferred.

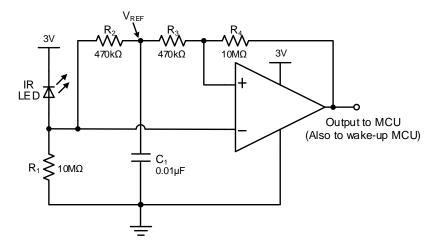

Figure 18 shows the detailed circuit design. The circuit establishes a threshold through R<sub>2</sub> and C<sub>1</sub> which automatically adapts to the ambient light level. To further reduce BOM cost, this example uses an IR LED as the IR receiver. The IR LED is reverse-biased to function as a photodiode (but at a reduced sensitivity).

The low input bias current allows a greater load resistor value (R<sub>1</sub>) without sacrificing linearity, which in turn helps reduce the always-on supply current.

The load resistor  $R_1$  converts the IR light induced current into a voltage fed into the inverting input of the comparator.  $R_2$  and  $C_1$  establish a reference voltage  $V_{REF}$  which tracks the mean amplitude of the IR signal. The non-inverting input is

connected to  $V_{REF}$  through R<sub>3</sub>. And finally R<sub>3</sub> and R<sub>4</sub> are used to introduce additional hysteresis to keep the output free of spurious toggles.

Figure 18. IR Receiver AFE Using GD30CP331/GD30CP393

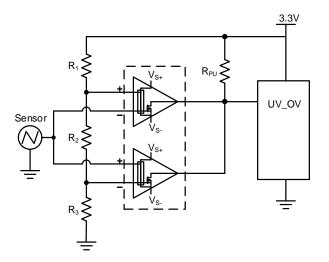

## 7.2 Window Comparator

Window comparators are commonly used to detect undervoltage (UV) and overvoltage (OV) conditions. Figure 19 shows a simple window comparator circuit.

Figure 19. Window Comparator

For this design, follow these design requirements:

- Alert (logic low output) when an input signal is less than 1.1V

- Alert (logic low output) when an input signal is greater than 2.2V

- Alert signal is active low

- Operate from a 3.3V power supply

Configure the circuit as shown in Figure 19. Connect  $V_{S+}$  to a 3.3V power supply and  $V_{S-}$  to ground. Make  $R_1$ ,  $R_2$  and  $R_3$  each 10M $\Omega$  resistors. These three resistors are used to create the positive and negative thresholds for the window comparator ( $V_{TH+}$  and  $V_{TH-}$ ). With each resistor being equal,  $V_{TH+}$  is 2.2V and  $V_{TH-}$  is 1.1V. Large resistor values such as 10M $\Omega$  are used to minimize power consumption. The sensor output voltage is applied to

www.gigadevice.com

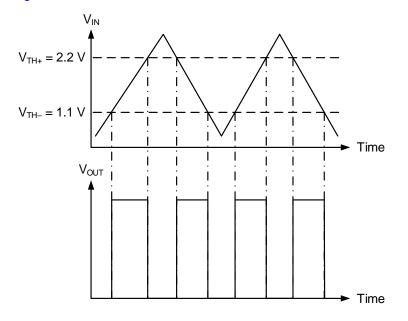

the inverting and non-inverting inputs of the 2-channel GD30CP331/GD30CP393's. The GD30CP331/GD30CP393 is used for its open-drain output configuration. Using the GD30CP331/GD30CP393 allows the two comparator outputs to be Wire-ORed together. The respective comparator outputs will be low when the sensor is less than 1.1V or greater than 2.2V.  $V_{OUT}$  will be high when the sensor is in the range of 1.1V to 2.2V. See the application curve in Figure 20.

Figure 20. Window Comparator Results

# 8 Package Information

## 8.1 Outline Dimensions

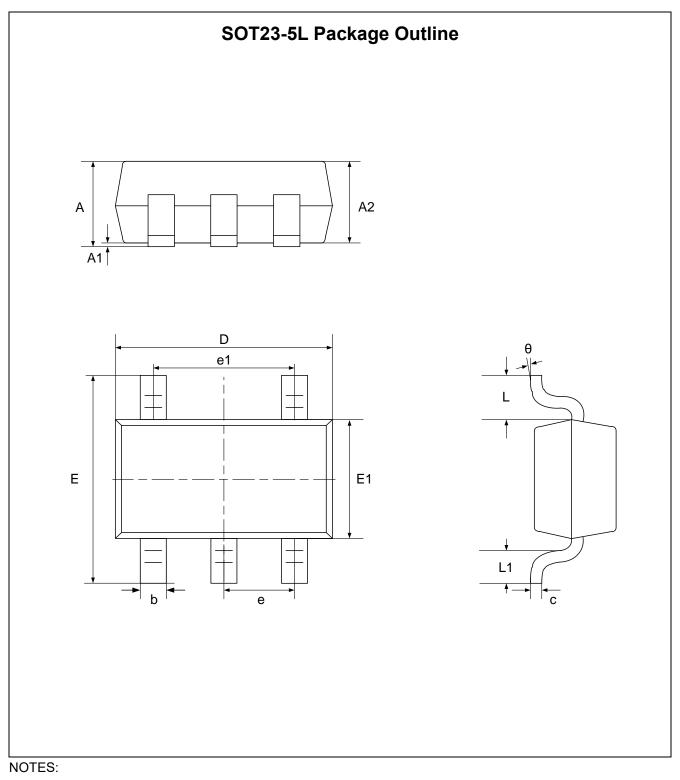

- 1. All dimensions are in millimeters.

- 2. Package dimensions does not include mold flash, protrusions, or gate burrs.

- 3. Refer to the Table 1 SOT23-5L dimensions(mm).

#### Table 1. SOT23-5L dimensions(mm)

| SYMBOL | MIN   | NOM      | MAX   |  |  |

|--------|-------|----------|-------|--|--|

| A      |       |          | 1.35  |  |  |

| A1     | 0.00  |          | 0.15  |  |  |

| A2     | 1.00  |          | 1.20  |  |  |

| b      | 0.35  |          | 0.45  |  |  |

| С      | 0.14  |          | 0.20  |  |  |

| D      | 2.82  |          | 3.02  |  |  |

| E      | 2.60  |          | 3.00  |  |  |

| E1     | 1.526 |          | 1.726 |  |  |

| е      |       | 0.95 BSC |       |  |  |

| e1     |       | 1.90 BSC |       |  |  |

| L      |       | 0.60 REF |       |  |  |

| L1     | 0.30  |          | 0.60  |  |  |

| θ      | 0°    |          | 8°    |  |  |

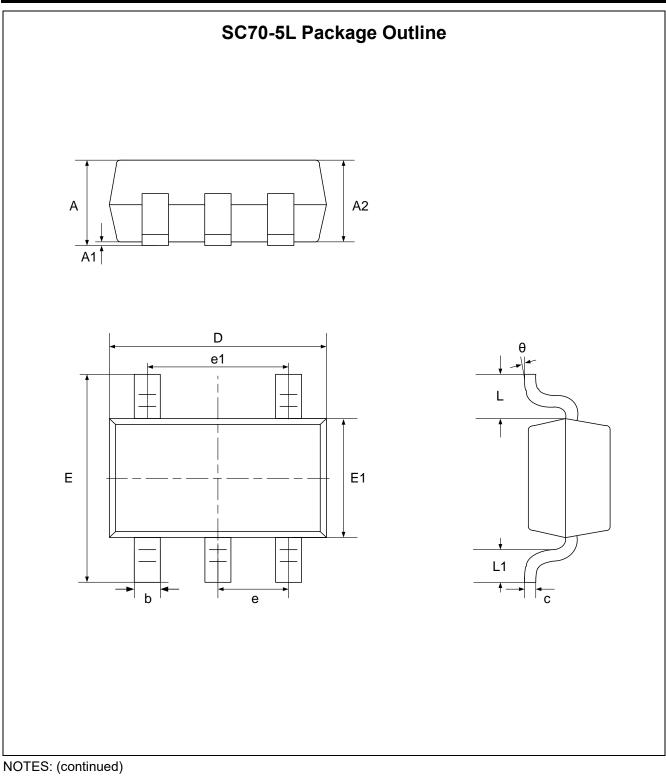

1. Refer to the Table 2 SC70-5L dimensions(mm).

#### Table 2. SC70-5L dimensions(mm)

| SYMBOL | MIN       | NOM      | MAX  |  |

|--------|-----------|----------|------|--|

| A      | 0.90      |          | 1.10 |  |

| A1     | 0.00      |          | 0.10 |  |

| A2     | 0.90      |          | 1.00 |  |

| b      | 0.15      |          | 0.35 |  |

| с      | 0.08      |          | 0.15 |  |

| D      | 2.00      |          | 2.20 |  |

| E      | 2.15      |          | 2.45 |  |

| E1     | 1.15      |          | 1.35 |  |

| e      |           | 0.65 BSC |      |  |

| e1     |           | 1.30 BSC |      |  |

| L      | 0.525 REF |          |      |  |

| L1     | 0.26      |          | 0.46 |  |

| θ      | 0°        |          | 8°   |  |

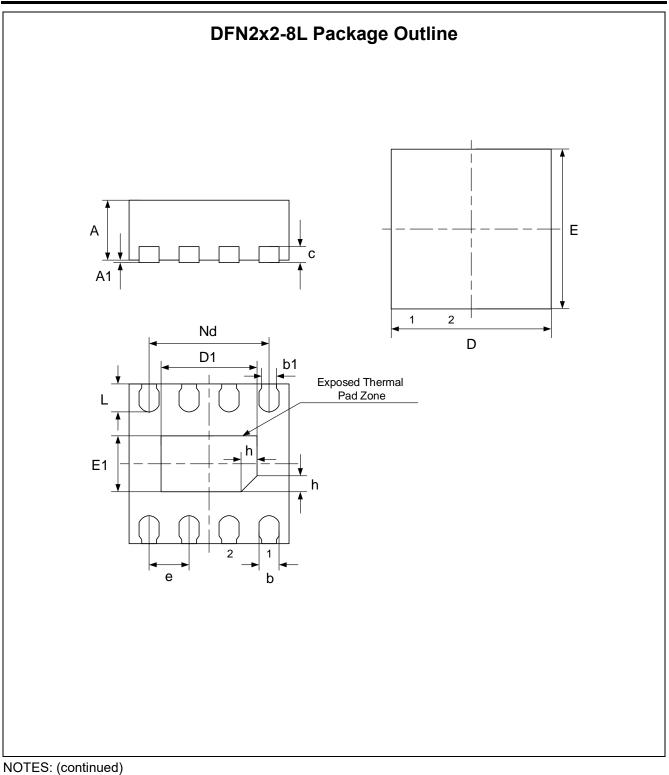

1. Refer to the Table 3 *DFN2x2-8L dimensions(mm)*.

#### Table 3. DFN2x2-8L dimensions(mm)

| SYMBOL | MIN      | NOM      | MAX  |  |

|--------|----------|----------|------|--|

| A      | 0.70     | 0.75     | 0.80 |  |

| A1     |          | 0.02     | 0.05 |  |

| b      | 0.20     | 0.25     | 0.30 |  |

| b1     |          | 0.18 REF |      |  |

| С      | 0.18     | 0.20     | 0.25 |  |

| D      | 1.90     | 2.00     | 1.30 |  |

| D1     | 1.10     | 1.20     | 1.30 |  |

| Nd     |          | 1.50 BSC |      |  |

| E      | 1.90     | 2.00     | 2.10 |  |

| E1     | 0.60     | 0.70     | 0.80 |  |

| e      | 0.50 BSC |          |      |  |

| L      | 0.30     | 0.35     | 0.40 |  |

| h      | 0.15     | 0.20     | 0.25 |  |

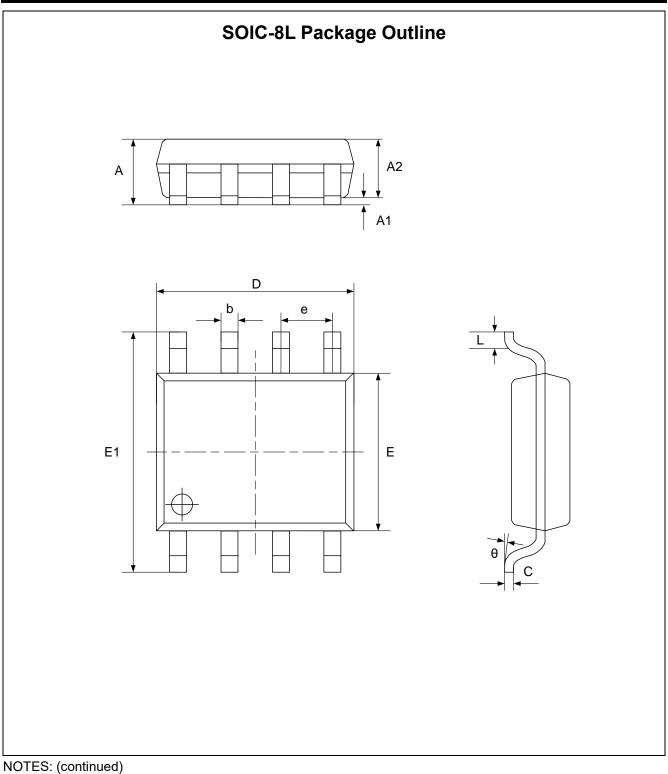

1. Refer to the Table 4 SOIC-8L dimensions(mm).

#### Table 4. SOIC-8L dimensions(mm)

| SYMBOL | MIN   | NOM   | MAX   |

|--------|-------|-------|-------|

| A      | 1.370 |       | 1.670 |

| A1     | 0.070 |       | 0.170 |

| A2     | 1.300 |       | 1.500 |

| b      | 0.306 |       | 0.506 |

| С      |       | 0.203 |       |

| D      | 4.700 |       | 5.100 |

| E      | 3.820 |       | 4.020 |

| E1     | 5.800 |       | 6.200 |

| е      |       | 1.270 |       |

| L      | 0.450 |       | 0.750 |

| θ      | 0°    |       | 8°    |

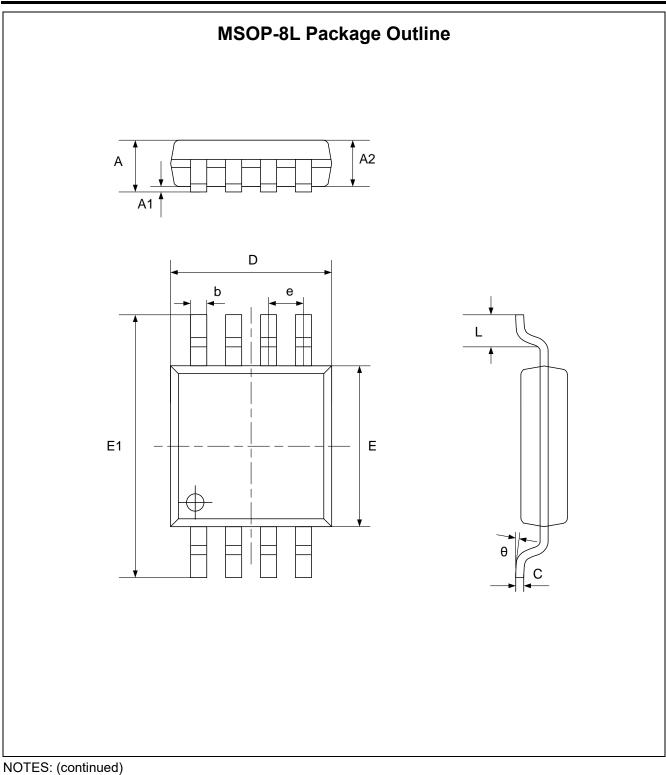

1. Refer to the Table 5 MSOP-8L dimensions(mm).

#### Table 5. MSOP-8L dimensions(mm)

| SYMBOL | MIN   | NOM   | MAX   |

|--------|-------|-------|-------|

| A      | 0.800 |       | 1.100 |

| A1     | 0.050 |       | 0.150 |

| A2     | 0.750 |       | 0.950 |

| b      | 0.290 |       | 0.380 |

| С      | 0.150 |       | 0.200 |

| D      | 2.900 |       | 3.100 |

| E      | 2.900 |       | 3.100 |

| E1     | 4.700 |       | 5.100 |

| е      |       | 0.650 |       |

| L      | 0.400 |       | 0.700 |

| θ      | 0°    |       | 8°    |

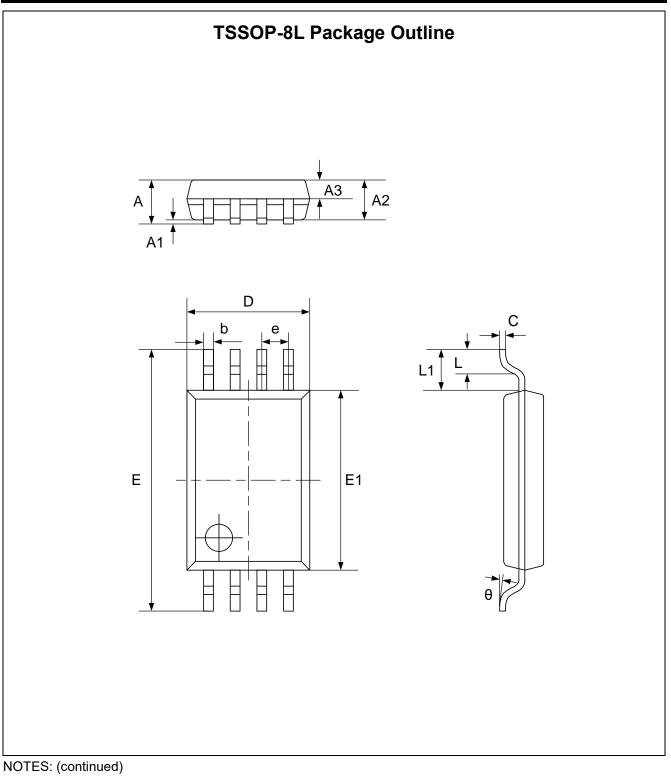

1. Refer to the Table 6 *TSSOP-8L dimensions(mm)*.

#### Table 6. TSSOP-8L dimensions(mm)

| SYMBOL | MIN   | NOM       | MAX   |

|--------|-------|-----------|-------|

| A      |       |           | 1.200 |

| A1     | 0.020 |           | 0.150 |

| A2     | 0.900 |           | 1.050 |

| A3     | 0.390 |           | 0.490 |

| b      | 0.200 |           | 0.290 |

| С      | 0.130 |           | 0.180 |

| D      | 2.900 |           | 3.100 |

| E      | 6.200 |           | 6.600 |

| E1     | 4.300 |           | 4.500 |

| e      |       | 0.650     |       |

| L1     |       | 1.000 REF |       |

| L      | 0.450 |           | 0.750 |

| θ      | 0°    |           | 8°    |

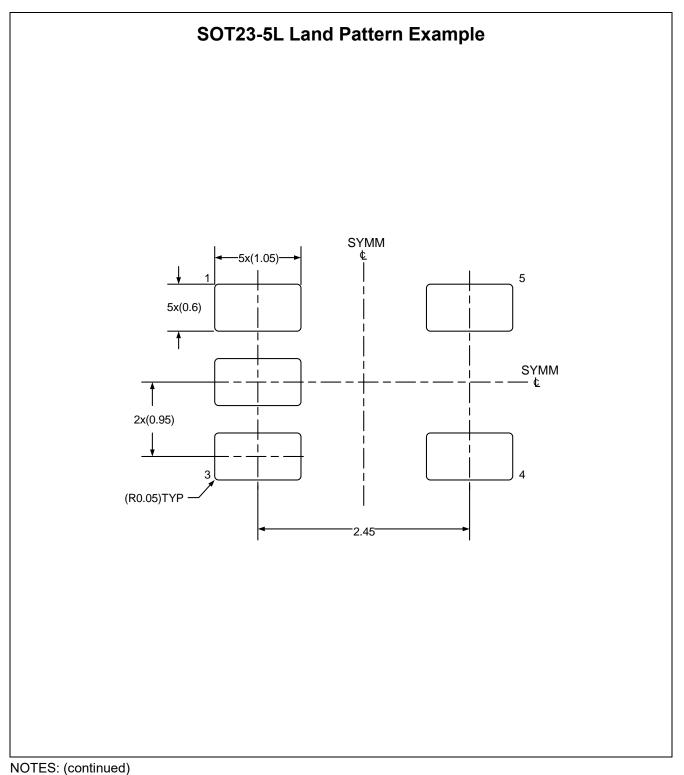

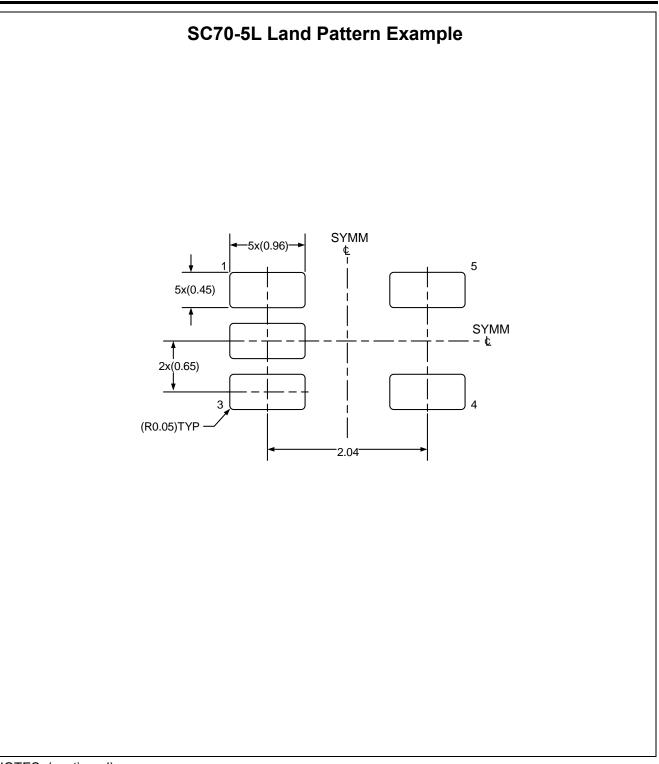

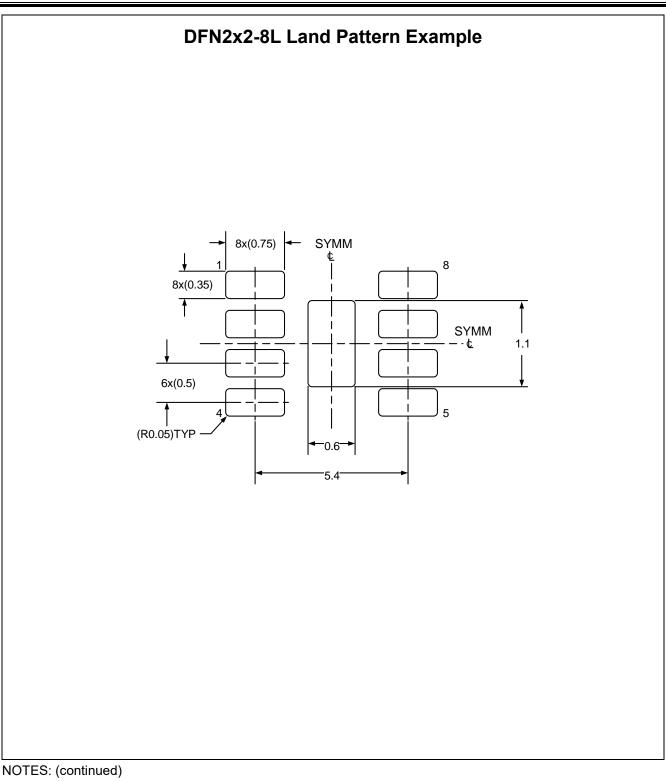

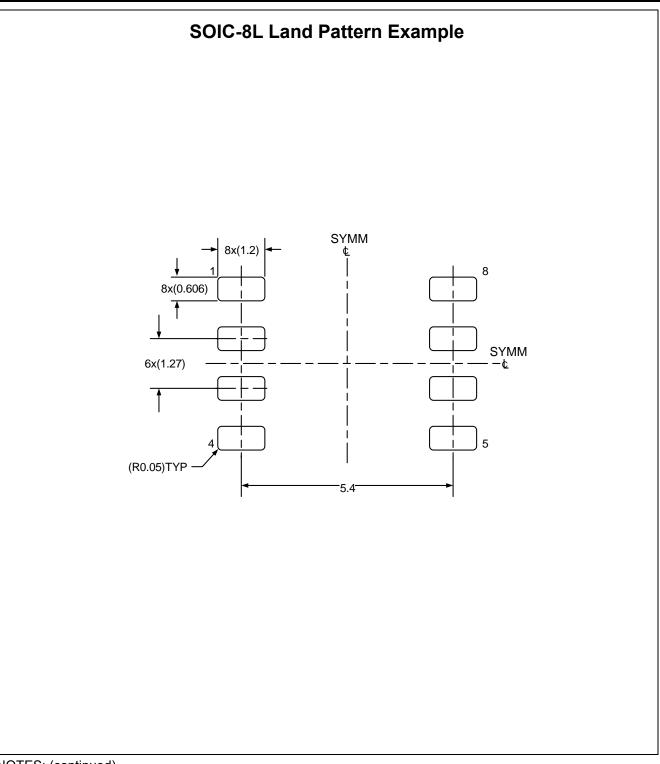

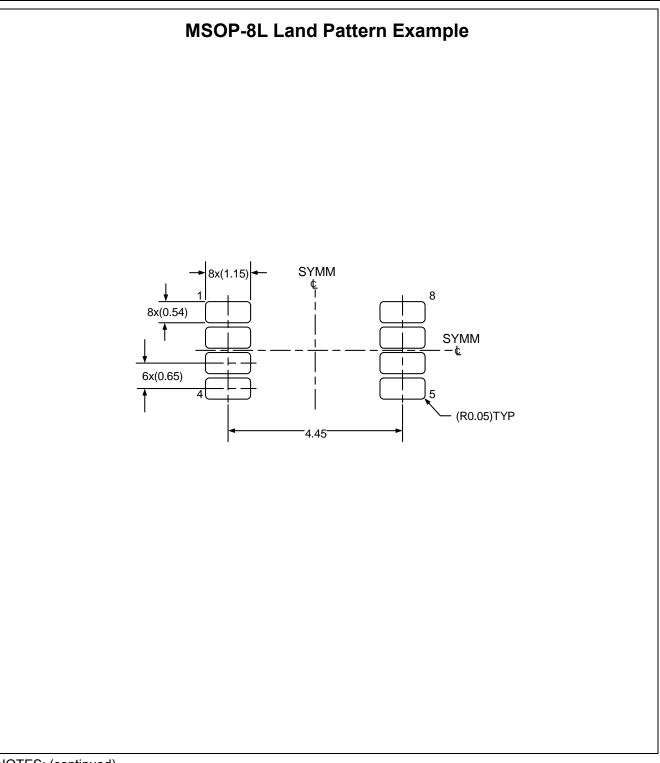

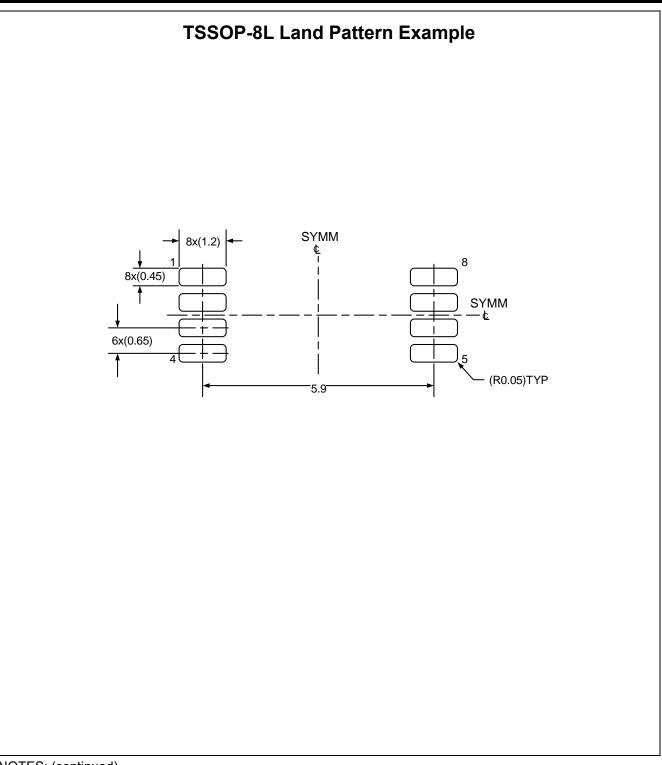

## 8.2 Recommended Land Pattern

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 20X scale.

NOTES: (continued)

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 20X scale.

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 20X scale.

- NOTES: (continued)

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 10X scale.

- NOTES: (continued)

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 10X scale.

- NOTES: (continued)

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 10X scale.

# 9 Ordering Information

| Ordering Code    | Package Type | ECO Plan | Packing Type | MOQ  | OP Temp(°C)     |

|------------------|--------------|----------|--------------|------|-----------------|

| GD30CP331ANSTR-K | SOT23-5L     | Green    | Tape & Reel  | 3000 | -40°C to +125°C |

| GD30CP331ANDTR-K | SC70-5L      | Green    | Tape & Reel  | 3000 | -40°C to +125°C |

| GD30CP331ANSTR-R | SOT23-5L     | Green    | Tape & Reel  | 3000 | -40°C to +125°C |

| GD30CP393AWLTR-K | SOIC-8L      | Green    | Tape & Reel  | 4000 | -40°C to +125°C |

| GD30CP393AWMTR-K | MSOP-8L      | Green    | Tape & Reel  | 3000 | -40°C to +125°C |

| GD30CP393AWPTR-K | TSSOP-8L     | Green    | Tape & Reel  | 3000 | -40°C to +125°C |

| GD30CP393AWETR-K | DFN2x2-8L    | Green    | Tape & Reel  | 3000 | -40°C to +125°C |

# **10 Revision History**

| REVISION NUMBER | DESCRIPTION                                          | DATE |

|-----------------|------------------------------------------------------|------|

| 1.0             | Initial release and device details                   | 2023 |

| 1.1             | Modify ambient operating temperature +85°C to +125°C | 2024 |

## **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company according to the laws of the People's Republic of China and other applicable laws. The Company reserves all rights under such laws and no Intellectual Property Rights are transferred (either wholly or partially) or licensed by the Company (either expressly or impliedly) herein. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no representations or warranties of any kind, express or implied, with regard to the merchantability and the fitness for a particular purpose of the Product, nor does the Company assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the sole responsibility of the user of this document to determine whether the Product is suitable and fit for its applications and products planned, and properly design, program, and test the functionality and safety of its applications and products planned using the Product. Unless otherwise expressly specified in the datasheet of the Product, the Product is designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only, and the Product is not designed or intended for use in (i) safety critical applications such as weapons systems, nuclear facilities, atomic energy controller, combustion controller, aeronautic or aerospace applications, traffic signal instruments, pollution control or hazardous substance management; (ii) life-support systems, other medical equipment or systems (including life support equipment and surgical implants); (iii) automotive applications or environments, including but not limited to applications for active and passive safety of automobiles (regardless of front market or aftermarket), for example, EPS, braking, ADAS (camera/fusion), EMS, TCU, BMS, BSG, TPMS, Airbag, Suspension, DMS, ICMS, Domain, ESC, DCDC, e-clutch, advancedlighting, etc.. Automobile herein means a vehicle propelled by a self-contained motor, engine or the like, such as, without limitation, cars, trucks, motorcycles, electric cars, and other transportation devices; and/or (iv) other uses where the failure of the device or the Product can reasonably be expected to result in personal injury, death, or severe property or environmental damage (collectively "Unintended Uses"). Customers shall take any and all actions to ensure the Product meets the applicable laws and regulations. The Company is not liable for, in whole or in part, and customers shall hereby release the Company as well as its suppliers and/or distributors from, any claim, damage, or other liability arising from or related to all Unintended Uses of the Product. Customers shall indemnify and hold the Company, and its officers, employees, subsidiaries, affiliates as well as its suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Product.

Information in this document is provided solely in connection with the Product. The Company reserves the right to make changes, corrections, modifications or improvements to this document and the Product described herein at any time without notice. The Company shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 GigaDevice – All rights reserved